Sisällysluettelo:

- Kirjoittaja John Day day@howwhatproduce.com.

- Public 2024-01-30 08:59.

- Viimeksi muokattu 2025-06-01 06:09.

JDM on suosittu PIC -ohjelmoija, koska se käyttää sarjaporttia, minimikomponentteja eikä vaadi virtalähdettä. Mutta siellä on hämmennystä, ja verkossa on monia ohjelmoijamuunnelmia, mitkä toimivat minkä PIC: n kanssa? Tässä "ohjeellisessa" me testasimme JDM: n ja minä näytän kuinka simuloida piiriä käyttämällä Spiceä, joka vastaa kaikkiin kysymyksiisi!

Tarvikkeet

LTspice, jonka voit ladata analogisista laitteista täältä.

Tarvitset myös JDM -piiritiedostot täällä.

Vaihe 1: Sarjaporttivaatimukset

JDM vaatii sarjaportin, joka täyttää EIA232-vaatimukset, mieluiten +12/-12 jännitetasolla.

Texas Instruments Line Driver MC1488 -lehden mukaan (kuva 3)

Lähtöimpedanssi = 4V/8mA = 500 ohmia.

Oikosulkuvirran raja = 12 mV, ilman aikarajaa - ei vaurioita sirulle.

Linjavastaanottimen tuloimpedanssi = 3-7 k ohmia suositellaan.

Vanhempien pöytätietokoneiden sarjaportit käyttävät +12v/-12V, jotka täyttävät tämän vaatimuksen.

Uusimpien kannettavien tietokoneiden sarjaportit käyttävät pienempää jännitettä. JDM voi toimia tai ei - vastaus on monimutkaisempi.

Vaihe 2: PIC -ohjelmointivaatimukset

PIC -ohjelmointivaatimuksia koskevat tiedot saadaan Microchipiltä. Yllä oleva koskee tyypillistä laitetta.

Vaihe 3: JDM -määritys

Onko alkuperäinen JDM -verkkosivusto kadonnut ajan kanssa? Tämä jättää meidät arvaamaan, mitä suunnittelija alun perin tarkoitti eritelmään.

- Tarjoa VDD = 5V ja enintään IDD = 2mA ("in socket" -versiossa)

- Anna VHH = 13 V ja enintään IHH = 0,2 mA.

- MCLR Nousuaika tVHHR = 1uS max.

- ICSP-version on pystyttävä vetämään MCLR matalalla 22 k vetovoimaa vastaan.

Vaihe 4: Piirin kuvaus

Kuva JDM1 perustuu "vakio" JDM -piiriin, joka on otettu PICPgm -verkkosivustolta. Tämä on “PIC in Socket” -ohjelmoija, jossa PIC ottaa virran TX- ja RTS -nastoista. Alkuperäistä kaaviota oli vaikea ymmärtää, joten olen piirtänyt sen uudelleen käyttämällä normaalia virtavirtausta ylhäältä alas. Lisäksi olen lisännyt LED -merkkivalot “RESET”, “PROG” ja “RTS”, joita tarvitaan rakentamisen ja testauksen aikana. Toivottavasti näillä ei ole haitallista vaikutusta käyttäytymiseen.

Piirisuunnittelun normaali käytäntö on yhteinen kaikille perusteille, mutta JDM: n keskeinen piirre on, että sarjaportin maa (GND) on kytketty VDD: hen. Tämä aiheuttaa sekaannusta, kun sarjaporttisignaaleja mitataan suhteessa GND-, PIC -signaaleihin suhteessa loogiseen maahan (VSS).

Kun TX nousee korkealle, Q1 toimii kahdena eteenpäin suuntautuneena diodina. (Q1 -keräin ei ole taaksepäin painotettu kuten normaalissa transistorikäytössä). Q1 -keräin lataa C2: n, jonka Zener (D3) puristaa VDD+8V: n jännitteellä. Q1 -lähetin toimittaa 13 V: n MCLR: lle ohjelmointi-/tarkistustilaa varten.

Kun TX laskee sen, kondensaattori C3 ladataan D1: n kautta ja ZS (D5) puristaa VSS: n jännitteeseen VDD-5V. Myös TX on kiinnitetty (VSS-0.6) D1: llä. Q1 on pois päältä, C1 varaa seuraavan ohjelmointipulssin. MCLR on kiinnitetty 0V: n D2: llä, joten PIC on nyt nollattu.

Kun RTS on korkea, kello lähetetään PGC: lle. D4 -puristin PGC korkealla VDD -logiikalla. Kun RTS on alhainen, kondensaattori C3 ladataan D6: n kautta ja ZS (D5) kiinnittää VSS: n jännitteeseen VDD-5V. D6 kiinnittää PGC: n VSS: ssä tai logiikassa 0.

Ohjelmoinnin aikana DTR: lle lähetetty data luetaan PGD: llä, jonka PIC määrittää tuloksi. Kun DTR on korkea, Q2 toimii "emitterin seuraajana" ja PGD-jännite on noin (VDD-0,6) tai logiikka 1. Kun DTR on alhainen, Q2 toimii huonona transistorina (lähetin ja keräimen nastat päinvastaiset). Q2 laskee PGD: n matalalle, jonka D7 puristaa VSS: ssä tai logiikassa 0.

Vahvistuksen aikana PIC määrittää PGD: n tulostettavaksi tiedonsiirtoon sarjaporttiin. DTR on asetettava korkealle ja tiedot luetaan CTS: llä. Kun PGD -lähtö on korkea, Q2 on pois päältä, CTS = DTR = +12V. Kun PGD -lähtö on alhainen, Q2 on päällä. Q2 -keräin imee virran (12V+5V)/(1k+1k5) = 7mA DTR: stä ja vetää CTS alhaiseksi VSS: ään.

Vaihe 5: Valmistaudu simulaatioon

Lataa LT -mauste, tallenna ja avaa täällä olevat piiritiedostot (*.asc). Piirin simuloimiseksi meidän on annettava sille joitain tuloja ja "jäljitettävä" lähdöt. V1, V2 V3 simuloivat 12 V: n sarjaporttia lähtöimpedanssilla R11, R12, R13.

- V1 tuottaa kaksi ohjelmapulssia TX: ssä 0,5 ms - 4,5 ms

- V2 tuottaa datapulssien purskeen DTR: ssä 1,5 - 4,5 ms

- V3 tuottaa kellopulssien purskeen RTS: llä 0,5 - 3,5 ms

Komponentit V4, X1, R15 ja R16 ovat kaikki osa simulaatiota.

- V4 tuottaa 2 pulssia 2,5 - 4,5 ms tietojen tarkistamiseksi.

- Hyppyjohdin X1 simuloi PGD: n LÄHTÖÄ.

- R15, R16 simuloivat PIC: n "lataamista" VDD: lle ja MCLR: lle.

Vaihe 6: Muutokset ICSP: lle

Kuva JDM3 näyttää "piirissä" -ohjelmoinnin version. Muutokset alkuperäisestä ovat

- Vaihda ZIF -liitäntä ICSP -liittimeen.

- PIC saa nyt virran kohdepiiristä (V5).

- Irrota 5V zener (D5).

- Pieni 100 pF: n kondensaattori (C4) siirretään kohdepiirin PIC: n viereen.

- LEDit ottavat virran piirilevyltä mahdollisuuksien mukaan.

- Kohdepiirissä tarvitaan MCLR-vetovastus (R10) ja diodi (D10).

- VAROITUS. Kohdetaulussa on oltava "kelluva" virtalähde, mieluiten akku.

- Älä liitä kohdemaata (VSS) tietokoneeseen/PC -maahan kytkemällä muita tietokoneportteja samaan aikaan kuin JDM.

JDM1: n simuloinnin jälkeen C2: n pitkän latausajan ongelma tuli ilmeiseksi. Sitten Fruttenboelin lukemisen jälkeen näyttää siltä, että C2 ja Q1 lisättiin muutoksena alkuperäiseen. En voi ajatella, mitä C2: n ja Q1: n tarkoitus on tehdä ongelmien luomisen lisäksi. Joten JDM4: ssä palaamme Fruttenboelin vanhempaan muotoiluun, joka on yksinkertainen ja yksinkertainen ymmärtää. D1 ja D3/LED2 puristin MCLR VSS: n ja VDD+8V: n välillä. R1: n arvo on pienennetty 3 k3: een, mikä riittää valaisemaan LED2 12 V: n jännitteellä.

JDM4 on myös suunniteltu toimimaan heikompien sarjaporttien kanssa. Kun TX nousee korkealle (+9 V), TX-virtalähde = (9-8)/(1k +3k3) = 0,2 mA, juuri niin paljon, että se voi nostaa MCLR: n korkealle, vaikka se ei riitä valaisemaan LED2: ta. Kun TX laskee (noin -7V), TX -virran hajautus = (9-7)/1k = 2mA. LED1-virta = (7-2 ledille)/(2k7) = 1,8 mA. MCLR-alasvetovirta = 7-5,5/3k3 = 0,5 mA.

Tätä piiriä on myös testattu (JDM5-simulointi) nähdäksemme, mitä tapahtuu +/- 7V: n sarjaporteille, joissa jännite ei riitä ylläpitämään VHH = 13V. C1: n tarkoitus tulee nyt ilmeiseksi, C1 luo lyhyen +ve -lisäyksen MCLR: ään, 33us piikkiin TX: n nousevassa reunassa, riittävän kauan, jotta PIC voi siirtyä ohjelmointitilaan. Mutta poista hyppyjohdin X2 (poista LED1 käytöstä), koska virta ei riitä MCLR: n pienentämiseen ja LED1: n sytyttämiseen. Kun TX laskee, TX-virranpoisto = (7V-5,5V)/(1k+3k3) = 0,3mA, riittää vetämään MCLR: n alhaiseksi ylösvetoa R10 vastaan.

Vaihe 7: Simulaatiotulokset

Voit tarkastella grafiikkatiedostoja napsauttamalla alla olevia linkkejä hiiren kakkospainikkeella ja valitsemalla sitten "Avaa linkki uudella välilehdellä".

Simulaatio 1: MCLR: n, VSS: n ja RTS: n jälki alkuperäiselle JDM1: lle. Havainnot 1, 2 ja 3 näkyvät välittömästi.

Simulaatio 2: MCLR: n ja VSS: n jälki ja RTS modifioidulle JDM2: lle, mikä korjaa aiemmat ongelmat.

Simulaatio 3: PGD: n, VSS: n ja PGC: n jälki JDM2: lle lähetettäessä tietoja ohjelmatilassa. Havainto 4 3,5 mS.

Simulaatio 4: PGD: n, VSS: n ja CTS: n jälki JDM2: lle tarkistustilassa (hyppyjohdin X1 lisätty). OK

Simulaatio 5: MCLR: n, VSS: n, PGD: n ja PGC: n jälki JDM3: lle. ICSP käyttää virtapiiriä ratkaisee monia ongelmia.

Simulaatio 6: MCLR: n, VSS: n, PGD: n ja PGC: n jälki JDM4: lle +/- 9V sarjaportilla. MCLR nousee välittömästi, täysin toimiva.

Simulaatio 7: MCLR: n, VSS: n ja TX: n jälki JDM5: lle +/- 7V sarjaportti ja hyppyjohdin X2 poistettu. C1 luo +ve boostin (piikin) MCLR: n nousevalle reunalle, melkein tarpeeksi työntämään MCLR: n TX: n yläpuolelle 13 V: iin.

Vaihe 8: Johtopäätökset

Spice on todella hyvä paljastamaan piirin toiminnan "piilotetut salaisuudet". Ilmeisesti JDM -piiri toimii ja on yhteensopiva monien PIC -sirujen kanssa, mutta seuraavat havainnot paljastavat mahdollisia rajoituksia/yhteensopivuusongelmia/vikoja?

- MCLR: n pitkä nousuaika, kun taas C2 latautuu VPP: lle TX: n ensimmäisellä pulssilla. Epäonnistuu erittelyssä 3.

- Sarjaportti lataa C2, kun TX nousee korkealle ja RTS laskee. Mutta RTS: llä on myös tehtävä ladata C3. Kun molemmat tapahtuvat samanaikaisesti, tämä lisää kuormitusta RTS: lle, joten C3 menettää latauksen (VSS nousee) 2 ms: n simuloinnissa. Epäonnistuu eritelmässä 1.

- C3 menettää latauksen (VSS alkaa nousta) kellopulssien pysähtyessä 3,5 ms: iin.

- Mikä on C2: n tarkoitus, tarvitaanko sitä ollenkaan?

Ratkaisut

- Oletettavasti PICPgm käyttää”kierrosta” ohjelmistoa. Sen täytyy käyttää pitkää lähetyspulssia esilataukseen C2: een ja siirtyä ohjelmointitilaan vasta toisen lähetyspulssin jälkeen? Simulointia varten pienensin C2 -arvon 1uF: ksi, jotta nousuaika olisi 1 ms. Ei ihanteellinen ratkaisu.

- Jaa C2 ja C3, jotta ne latautuvat itsenäisesti. Yksi pieni muutos JDM2: een, C2: een viitataan GND: hen VSS: n sijasta.

- Ratkaisija JDM3. ICSP on paljon luotettavampi, koska PIC saa virtansa kohdepiiristä.

- JDM4 ratkaisee ongelman 1. Tämä on yksinkertainen rakenne, joka poistaa C2: n kokonaan.

Vaihe 9: Ja lopuksi

Todiste vanukasta on syömisessä. Tämä JDM toimii, joten käytä sitä edelleen.

Ja suositukseni ovat:

- käytä JDM2: ta pistorasian ohjelmointiin ja 12 V: n sarjaportteihin,

- käytä JDM4: ää ICSP-ohjelmointi- ja sarjaportteihin yli +/- 9V,

- käytä JDM4: ää ja hyppyjohdin X2 poistettuna sarjaportteihin yli +/- 7V.

Viitteet:

Analog Devices LT -mauste

picpgm

Fruttenboel

Seuraa lisää PIC-projekteja sly-cornerissa

Suositeltava:

DIY Raspberry Pi Downloadbox: 4 vaihetta

DIY Raspberry Pi Downloadbox: Löydätkö usein itsesi lataamasta suuria tiedostoja, kuten elokuvia, torrentteja, kursseja, TV -sarjoja jne., Niin tulet oikeaan paikkaan. Tässä Instructable -ohjelmassa muuttaisimme Raspberry Pi zero -laitteemme latauskoneeksi. Joka voi ladata minkä tahansa

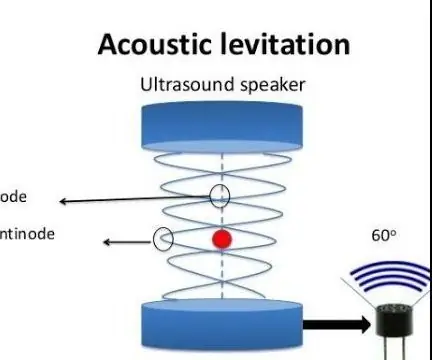

Akustinen levitaatio Arduino Unon kanssa Askel askeleelta (8 vaihetta): 8 vaihetta

Akustinen levitaatio Arduino Unon kanssa Askel askeleelta (8 vaihetta): ultraäänikaiuttimet L298N DC-naarasadapterin virtalähde urospuolisella dc-nastalla ja analogiset portit koodin muuntamiseksi (C ++)

4G/5G HD -videon suoratoisto DJI Dronesta alhaisella latenssilla [3 vaihetta]: 3 vaihetta

![4G/5G HD -videon suoratoisto DJI Dronesta alhaisella latenssilla [3 vaihetta]: 3 vaihetta 4G/5G HD -videon suoratoisto DJI Dronesta alhaisella latenssilla [3 vaihetta]: 3 vaihetta](https://i.howwhatproduce.com/images/009/image-25904-j.webp)

4G/5G HD -videon suoratoisto DJI Dronesta alhaisella latenssilla [3 vaihetta]: Seuraava opas auttaa sinua saamaan live-HD-videovirtoja lähes mistä tahansa DJI-dronesta. FlytOS -mobiilisovelluksen ja FlytNow -verkkosovelluksen avulla voit aloittaa videon suoratoiston droonilta

Pultti - DIY -langaton latauskello (6 vaihetta): 6 vaihetta (kuvilla)

Pultti - DIY -langaton latausyökello (6 vaihetta): Induktiiviset lataukset (tunnetaan myös nimellä langaton lataus tai langaton lataus) on langattoman voimansiirron tyyppi. Se käyttää sähkömagneettista induktiota sähkön tuottamiseen kannettaville laitteille. Yleisin sovellus on langaton Qi -latauslaite

4 vaihetta akun sisäisen vastuksen mittaamiseksi: 4 vaihetta

4 vaihetta akun sisäisen vastuksen mittaamiseksi: Tässä on 4 yksinkertaista vaihetta, joiden avulla voit mitata taikinan sisäisen vastuksen