Sisällysluettelo:

- Kirjoittaja John Day day@howwhatproduce.com.

- Public 2024-01-30 09:02.

- Viimeksi muokattu 2025-01-23 14:44.

Tämän projektin tavoitteena on luoda Smart Mirror -näytön toiminnallisuus. Peili näyttää ennusteet (aurinkoinen, osittain aurinkoinen, pilvinen, tuulinen, sade, ukkonen ja lumi) ja lämpötila -arvot -9999 ° -9999 °. Ennuste- ja lämpötila -arvot on koodattu kovalla tavalla ikään kuin matkivat niitä, kun ne jäsennellään sääsovellusliittymästä.

Projekti käyttää Zynq-Zybo-7000-korttia, jossa on FreeRTOS, ja käyttää Vivadoa 2018.2 laitteiston suunnitteluun ja ohjelmointiin.

Osat:

Zynq-Zybo-7000 (FreeRTOS)

19 LCD (640x480)

VGA -kaapeli

12 "x 18" akryylipeili

Vaihe 1: Vivadon määrittäminen

Lataa Vivado 2018.2 Xilinxistä ja käytä Webpack -lisenssiä. Käynnistä Vivado ja "Luo uusi projekti" ja anna sille nimi. Valitse seuraavaksi "RTL -projekti" ja "Älä määritä lähteitä tällä hetkellä". Kun valitset osaa, valitse "xc7z010clg400-1" ja napsauta "Valmis" seuraavalla sivulla.

Vaihe 2: Pakkaa VGA -ohjaimen IP

Lisää vga_driver.sv -tiedosto suunnittelulähteisiin. Napsauta sitten "Työkalut" ja valitse "Luo ja pakkaa uusi IP". Valitse "Pakkaa nykyinen projektisi". Valitse sitten IP -sijainti ja "Sisällytä.xci -tiedostot". Napsauta ponnahdusikkunassa "OK" ja sitten "Valmis".

Siirry "Pakkausvaiheet" -kohtaan "Tarkista ja pakkaa" ja valitse "Paketin IP".

Nyt vga_driverin pitäisi olla saatavilla IP -lohkona.

Vaihe 3: Zynq IP

Valitse IP -integraattori -osiosta Luo lohkosuunnittelu. Lisää "ZYNQ7 Processing System" ja kaksoisnapsauta lohkoa. Napsauta "Tuo XPS -asetukset" ja lataa ZYBO_zynq_def.xml -tiedosto.

Avaa seuraavaksi "PS-PL Configuration" -kohdasta "AXI Non Secure Enablement" -valikko ja valitse "M AXI GP0 -liitäntä".

Avaa sitten "MIO Configuration" -kohdasta "Application Processor Unit" -valikko ja tarkista "Timer 0" ja "Watchdog".

Avaa lopuksi "Kellon määritys" -kohdassa "PL Fabric Clocks" -valikko ja tarkista "FCLK_CLK0" ja 100 MHz.

Vaihe 4: GPIO IP

Lisää kaksi GPIO -lohkoa lohkon suunnitteluun. GPIO: ita käytetään pikselien osoitteen ja pikselien RGB -komponenttien ohjaamiseen. Määritä lohkot yllä olevien kuvien mukaisesti. Kun olet lisännyt ja määrittänyt molemmat lohkot, napsauta "Suorita yhteysautomaatio".

GPIO 0 - Kanava 1 ohjaa kuvapisteen osoitetta ja kanava 2 punaista väriä.

GPIO 1 - Kanava 1 ohjaa vihreää väriä ja kanava 2 ohjaa sinistä väriä.

Vaihe 5: Estä muisti

Lisää lohkomuistin generaattorin IP -esto lohkon suunnitteluun ja määritä yllä kuvatulla tavalla. Pikselivärit kirjoitetaan muistiosoitteisiin, jotka VGA -ohjain lukee. Osoiterivin on vastattava käytettävien pikselien määrää, joten sen on oltava 16 bittiä. Tiedot ovat myös 16 bittiä, koska niitä on 16 väribittiä. Emme välitä kuittausbittien lukemisesta.

Vaihe 6: Muu IP

Liitteenä oleva pdf -tiedosto näyttää valmistuneen lohkosuunnittelun. Lisää puuttuva IP ja viimeistele yhteydet. Myös "Tee ulkoiset" VGA -värilähtöille ja pystysuorille ja vaakasuorille synkronointilähdöille.

xlconcat_0 - Yhdistää yksittäiset värit yhdeksi 16 -bittiseksi RGB -signaaliksi, joka syötetään Block RAM -muistiin.

xlconcat_1 - Ketjuttaa sarake- ja rivisignaalit VGA -ohjaimesta ja syötetään lohkon RAM -muistin porttiin B. Tämän avulla VGA -ohjain voi lukea pikseliväriarvot.

VDD - Constant HIGH on kytketty Block RAM -laitteen kirjoitustoimintoon, jotta voimme aina olla oikeassa.

xlslice_0, 1, 2 - Viipaleita käytetään RGB -signaalin jakamiseen yksittäisiksi R-, G- ja B -signaaleiksi, jotka voidaan syöttää VGA -ohjaimeen.

Kun lohkon suunnittelu on valmis, luo HDL -kääre ja lisää rajoitustiedosto.

*Lohkosuunnittelu perustuu opaskirjaan, jonka on kirjoittanut benlin1994*

Vaihe 7: SDK

Tämän lohkon suunnittelua käyttävä koodi on alla. Init.c sisältää piirustusta käsittelevät toiminnot (ennusteet, luvut, asteen symboli jne.). Main.c: n pääsilmukka suoritetaan, kun levy on ohjelmoitu. Tämä silmukka asettaa ennuste- ja lämpötila -arvot ja kutsuu sitten piirtotoiminnot init.c. Se kiertää tällä hetkellä kaikki seitsemän ennustetta ja näyttää ne peräkkäin. On suositeltavaa lisätä katkaisupiste riville 239, jotta näet kaikki kuvat. Koodi kommentoidaan ja antaa sinulle lisätietoja.

Vaihe 8: Johtopäätös

Nykyisen projektin parantamiseksi voitaisiin ladata esiladattuja kuvia COE -tiedostoina Block Memory Generators -laitteisiin. Joten sen sijaan, että olisimme piirtäneet ennusteet manuaalisesti kuten C -koodissa, voisimme saada kuvat lukemaan. Yritimme tehdä tämän, mutta emme saaneet sitä toimimaan. Pystyimme lukemaan pikseliarvot ja tulostamaan ne, mutta se loi sotkuisia kuvia, jotka eivät olleet mitään sellaisia kuin ne, jotka latasimme RAM -muistiin. Block Memory Generator -lomake on hyödyllinen luettavaksi.

Projekti on pohjimmiltaan puoliksi älykäs peili, koska siitä puuttuu Internet -yhteys. Tämän lisääminen antaisi täydellisen Smart Mirrorin.

Suositeltava:

DIY Raspberry Pi Downloadbox: 4 vaihetta

DIY Raspberry Pi Downloadbox: Löydätkö usein itsesi lataamasta suuria tiedostoja, kuten elokuvia, torrentteja, kursseja, TV -sarjoja jne., Niin tulet oikeaan paikkaan. Tässä Instructable -ohjelmassa muuttaisimme Raspberry Pi zero -laitteemme latauskoneeksi. Joka voi ladata minkä tahansa

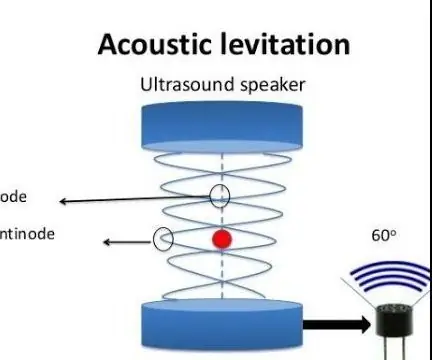

Akustinen levitaatio Arduino Unon kanssa Askel askeleelta (8 vaihetta): 8 vaihetta

Akustinen levitaatio Arduino Unon kanssa Askel askeleelta (8 vaihetta): ultraäänikaiuttimet L298N DC-naarasadapterin virtalähde urospuolisella dc-nastalla ja analogiset portit koodin muuntamiseksi (C ++)

4G/5G HD -videon suoratoisto DJI Dronesta alhaisella latenssilla [3 vaihetta]: 3 vaihetta

![4G/5G HD -videon suoratoisto DJI Dronesta alhaisella latenssilla [3 vaihetta]: 3 vaihetta 4G/5G HD -videon suoratoisto DJI Dronesta alhaisella latenssilla [3 vaihetta]: 3 vaihetta](https://i.howwhatproduce.com/images/009/image-25904-j.webp)

4G/5G HD -videon suoratoisto DJI Dronesta alhaisella latenssilla [3 vaihetta]: Seuraava opas auttaa sinua saamaan live-HD-videovirtoja lähes mistä tahansa DJI-dronesta. FlytOS -mobiilisovelluksen ja FlytNow -verkkosovelluksen avulla voit aloittaa videon suoratoiston droonilta

Pultti - DIY -langaton latauskello (6 vaihetta): 6 vaihetta (kuvilla)

Pultti - DIY -langaton latausyökello (6 vaihetta): Induktiiviset lataukset (tunnetaan myös nimellä langaton lataus tai langaton lataus) on langattoman voimansiirron tyyppi. Se käyttää sähkömagneettista induktiota sähkön tuottamiseen kannettaville laitteille. Yleisin sovellus on langaton Qi -latauslaite

4 vaihetta akun sisäisen vastuksen mittaamiseksi: 4 vaihetta

4 vaihetta akun sisäisen vastuksen mittaamiseksi: Tässä on 4 yksinkertaista vaihetta, joiden avulla voit mitata taikinan sisäisen vastuksen