Sisällysluettelo:

- Vaihe 1: PWM-moduulin lähdetiedoston luominen

- Vaihe 2: PWM-moduulin rakentaminen- Vivado-asennus

- Vaihe 3: PWM-moduulin rakentaminen- Luo projektitiedosto

- Vaihe 4: PWM-moduulin rakentaminen- lohkosuunnittelu ja rajoitustiedostoasetus (I)

- Vaihe 5: PWM-moduulin rakentaminen- lohkosuunnittelu ja rajoitustiedostoasetus (II)

- Vaihe 6: PWM-moduulin rakentaminen- lohkosuunnittelu ja rajoitustiedostoasetus (III)

- Vaihe 7: PWM-moduulin rakentaminen- lohkosuunnittelu ja rajoitustiedostoasetus (IV)

- Vaihe 8: PWM-moduulin rakentaminen- lohkosuunnittelu ja rajoitustiedostoasetus (V)

- Vaihe 9: PWM-moduulin rakentaminen- laitteiston asennus

- Vaihe 10: PWM-moduulin rakentaminen- Luo bittivirta ja käynnistä SDK

- Vaihe 11: PWM-moduulin rakentaminen- Luo uusi sovellus Xilinx SDK: ssa

- Vaihe 12: PWM-moduulin rakentaminen- Project Explorerin yleiskatsaus (I)

- Vaihe 13: PWM-moduulin rakentaminen- Project Explorerin yleiskatsaus (II)

- Vaihe 14: PWM-moduulin rakentaminen- Project Explorerin yleiskatsaus (III)

- Vaihe 15: PWM-moduulin rakentaminen- PWM-toiminto (I)

- Vaihe 16: PWM-moduulin rakentaminen- PWM-toiminto (II)

- Vaihe 17: PWM-moduulin rakentaminen- PWM-toiminto (III)

- Vaihe 18: PWM-moduulin rakentaminen- Suorita se

- Vaihe 19: Videon käsittelyn suoratoisto Digilent ZYBO: ssa OV7670: n avulla

- Vaihe 20: Täytä lohkokaavio

- Vaihe 21: Liitä OV7670 ZYBO -laitteeseen

- Vaihe 22: Luo lohkosuunnittelu

- Vaihe 23: Lisää VHDL -tiedostoja OV7670 -kameran hallintaan ja sieppaukseen

- Vaihe 24: Lisää rajoitustiedosto

- Vaihe 25: Lisää IP Repo HLS IP: lle

- Vaihe 26: Lisää moduuleja ja IP

- Vaihe 27: IP -määritysasetukset

- Vaihe 28: Lisää ja määritä PS IP -esto

- Vaihe 29: Osa 1. PWM -moduulin rakentaminen servomoottoreille

- Vaihe 30: Videotulon sivuliitännät (korostettu)

- Vaihe 31: Yhteydet OV7670: een

- Vaihe 32: Liitännät videolähtöpuolella

- Vaihe 33: Suorita lohko- ja yhteysautomaatio

- Vaihe 34: Luo HDL -kääre

- Vaihe 35: Luo bittivirta, vie laitteisto SDK: hon, käynnistä SDK Vivadosta

- Vaihe 36: SDK (ei FreeRTOS)

- Vaihe 37: FreeRTOS -käyttöönotto

- Vaihe 38: Käyttöohjeet

- Vaihe 39: Viitteet ja linkit

- Kirjoittaja John Day day@howwhatproduce.com.

- Public 2024-01-30 09:03.

- Viimeksi muokattu 2025-01-23 14:44.

Aloita vaiheesta 1, jos haluat lisätietoja vain 2-akselisen servo-PWM-ohjaimen luomisesta.

Aloita koko projektin massiivisesta lohkokaaviosta (vaihe 19).

Käyttämämme kamera- ja panorointi-/kallistusasetukset:

Servojen yhdistämiseen käytettiin Digilentin PmodCON3 -laitetta.

Vaihe 1: PWM-moduulin lähdetiedoston luominen

Vaihe 2: PWM-moduulin rakentaminen- Vivado-asennus

Lataa ensin Vivado Design Suite Xilinx -verkkosivustolta. Asenna kaikki suunnittelupaketit, mukaan lukien Vivado Software Development Kit (SDK). Tämä projekti käyttää versiota 2017.2.

Sillä välin Digilent Adept 2 tulisi asentaa myös Zybo -levyn ohjaimeksi.

Vaihe 3: PWM-moduulin rakentaminen- Luo projektitiedosto

Ennen projektitiedoston luomista sinun on varmistettava, että olet jo asentanut Zybo -tiedoston oikein tässä opetusohjelmassa:

Vivado Versio 2015.1 ja uudemmat korttitiedostojen asennus

Avaa Vivado 2017.2. Napsauta pikakäynnistyksessä Luo projekti -> Seuraava -> Projektin nimi (Nimeä projektisi nimi täällä) -> Projektityyppi. Valitse Projektityyppi -kohdasta RTL -projekti ja valitse kohta Älä määritä lähteitä tällä hetkellä. Valitse seuraavaksi oletusosalle näyttönimeksi "Boards" ja "Zybo". Napsauta seuraavaksi Valmis aloittaaksesi projektin.

Vaihe 4: PWM-moduulin rakentaminen- lohkosuunnittelu ja rajoitustiedostoasetus (I)

Napsauta Flow Navigatorissa”” Luo lohkosuunnittelu”ja paina sitten OK. Lisää tarvittavat IP -osoitteet napsauttamalla "+" -merkkiä. Lisätä:

- Yksi ZYNQ7 -käsittelyjärjestelmä Kaksi AXI -ajastinta

- Kaksi AXI -ajastinta

Vaihe 5: PWM-moduulin rakentaminen- lohkosuunnittelu ja rajoitustiedostoasetus (II)

IP -osoitteiden lisäämisen jälkeen suorita lohkoautomaatio ja yhteysautomaatio. Kun automaatio on valmis, napsauta lohkossa "axi_timer_0" hiiren kakkospainikkeella pwm0 -> Tee ulkoinen. Nimeä pwm0 ulkoinen nasta muotoon pwm_Xaxis. Toista myös yllä oleva prosessi lohkossa "axi_timer_1" ja anna pwm0 -ulkoiselle nastalle nimi pwm_Zaxis.

Vaihe 6: PWM-moduulin rakentaminen- lohkosuunnittelu ja rajoitustiedostoasetus (III)

Huomaa, että joka kerta, kun lopetamme lohkosuunnittelun Vivadossa, meidän on luotava HDL -kääre. Koska se on kunkin hankkeen ylätason moduuli.

Vaihe 7: PWM-moduulin rakentaminen- lohkosuunnittelu ja rajoitustiedostoasetus (IV)

Nyt meidän on määritettävä rajoitustiedosto, jotta voimme määrittää lohkokaavioomme yhdistetyt nastat. Sulje Block Design -ikkunan Lähteet-välilehti, "Lisää lähteitä"-> Lisää tai luo rajoituksia-> lisää Zybo-Master.xdc rajoitustiedostoiksi.

Vaihe 8: PWM-moduulin rakentaminen- lohkosuunnittelu ja rajoitustiedostoasetus (V)

Avaa rajoitustiedosto Zybo-Master.xdc Rajoitukset-kansiosta, poista kommentit, jotka haluamme määrittää lähtösignaaleiksi, ja nimeä "get_ports {XXXX}", joka XXXX tarkoittaa lohkokaaviossa mainittua ulkoista pin-koodia. Rajoitetiedoston asetus näkyy kuvassa.

Vaihe 9: PWM-moduulin rakentaminen- laitteiston asennus

Liitä servomoottorit Pmod CON3 -laitteeseen. TowerPro SG90 on tässä projektissa käytetty servomoottorimalli. Servomoottorin johdoissa oranssi johto edustaa PWM -signaalia, joka on kytketty SIG -nastaan Pmod CON3: ssa. Punainen johto Vcc on virtajohto, joka on kytketty VS -nastaan Pmod CON3: ssa. Lopuksi ruskea johto Gnd on maajohto, joka on kytketty GND -nastaan. Aseta sitten Pmod CON3 Zybo Boardin JD -portin yläriville.

Vaihe 10: PWM-moduulin rakentaminen- Luo bittivirta ja käynnistä SDK

1. Suorita Project Navigator -välilehdessä Luo BitStream.

2. Viedä laitteisto: Tiedosto> Vie> Vie laitteisto-> merkitse "sisällytä bittivirta"-> OK 3. Käynnistä SDK: Tiedosto-> Käynnistä SDK.

Vaihe 11: PWM-moduulin rakentaminen- Luo uusi sovellus Xilinx SDK: ssa

Luo uusi sovellus:

Tiedosto> Uusi> Sovellusprojekti -> Anna projektisi nimi -> Valmis

Project Explorerissa pitäisi olla kolme kansiota.

Tässä tapauksessa "design_1_wrapper_hw_platform_0" on Vivadon aiemmin viemä kansio. Axis_2_PWM_SDK_bsp on hallituksen tukipakettikansio. Axis_2_PWM_SDK on tärkein projektikansio SDK: ssa. Näet "helloworld.c" -tiedoston Axis_2_PWM_SDK -kansion "src" -kansion alla, jossa "helloworld.c" on päätiedosto.

Vaihe 12: PWM-moduulin rakentaminen- Project Explorerin yleiskatsaus (I)

Tarkistetaan joitain tiedostoja Project Explorerissa. Avaa ensin kansio "design_1_wrapper_hw_platform_0" "system.hdf". Tämä tiedosto osoittaa prosessorin ps7_cortex9 osoitekortin ja suunnittelussamme olevat IP -lohkot.

Vaihe 13: PWM-moduulin rakentaminen- Project Explorerin yleiskatsaus (II)

Tarkista sitten "include" ja "libsrc" -tiedostot "Axis_2_PWM_SDK_bsp" -kansiosta. Kirjastotiedostojen avulla voimme olla vuorovaikutuksessa laitteisto -oheislaitteiden kanssa”toistamatta” rekistereitä.

Vaihe 14: PWM-moduulin rakentaminen- Project Explorerin yleiskatsaus (III)

BSP -dokumentaation kautta xtmrctr.h löytyy AXI -ajastimeen liittyvästä Xilinx -ajastimen ohjauskirjastosta. Yleensä voimme löytää halutun PWM -toiminnon täältä. Jos kuitenkin luet dokumentaation "tmrctr_v4_3", se osoittaa, että ohjain ei tällä hetkellä tue laitteen PWM -toimintaa. PWM -toiminnon puutteen vuoksi meidän on lopetettava PWM -toiminto xtmrctr.h ja AXI Timer v2.0 LogiCORE IP -tuoteoppaan avulla.

Vaihe 15: PWM-moduulin rakentaminen- PWM-toiminto (I)

Takaisin päätiedostoon "helloworld.c", sisällytä seuraavat otsikkotiedostot:

Vaihe 16: PWM-moduulin rakentaminen- PWM-toiminto (II)

Määritä kahden AXI TImerin tukiasemat osoitteessa xparameters.h.

Vaihe 17: PWM-moduulin rakentaminen- PWM-toiminto (III)

Luo haluttu PWM -toiminto.

Duty_val: muuntaa asteen arvon käyttöjaksoksi. PWM_Freq_Duty: aseta haluttu taajuus ja käyttöjakso PWM: n luomiseksi. Kellonaika on myös määritettävä.

PWM_START: määritä PWM -rekisteriosoite ja aloita PWM: n luominen.

PWM_STOP: määritä PWM -rekisteriosoite ja lopeta PWM: n luominen.

Loput demokoodit näkyvät "helloworld.c" -kohdassa kohdassa "Axis_2_PWM_SDK"

Vaihe 18: PWM-moduulin rakentaminen- Suorita se

1. ohjelmoi FPGA SDK: n kautta

- Liitä Zybo Board PC: hen USB -portin kautta.

- Xilinx -työkalut -> Ohjelmoi FPGA

2. Käynnistä ohjelma

Napsauta "Suorita" -kuvaketta ja pudota alas valikosta -> Suorita nimellä -> Käynnistä laitteistossa

3. SDK -pääte

- Avaa SDK -pääte -> Yhdistä sarjaporttiin -> OK

- Suorita ohjelma. Jos esittelykoodi suoritetaan onnistuneesti, näet "Alustus valmis!" SDK -terminaalissa.

Vaihe 19: Videon käsittelyn suoratoisto Digilent ZYBO: ssa OV7670: n avulla

Täydellinen arkistotiedosto liitteenä.

Vaihe 20: Täytä lohkokaavio

Tämä näyttää projektin kaikkien yhteyksien ja IP -lohkojen täydellisen kaavion

Vaihe 21: Liitä OV7670 ZYBO -laitteeseen

Luo yhteys ov7670 -moduulin kytkemiseen ZYBO Pmod -laitteisiin

Data Pmod on Pmod D.

Ohjaus Pmod on Pmod C.

Liitä lisäksi PmodCON3 ja servot tämän opetusohjelman ensimmäisessä puoliskossa kuvatulla tavalla

Vaihe 22: Luo lohkosuunnittelu

Napsauta Flow Navigatorissa "Luo lohkosuunnittelu" ja paina sitten OK.

Vaihe 23: Lisää VHDL -tiedostoja OV7670 -kameran hallintaan ja sieppaukseen

Lisää tähän vaiheeseen liitetyt VHDL -tiedostot projektiin

Vaihe 24: Lisää rajoitustiedosto

Lisää liitteenä oleva rajoitustiedosto projektiisi.

Vaihe 25: Lisää IP Repo HLS IP: lle

Ota liitteenä oleva Zip -tiedosto ja pura se uuteen kansioon, joka on nimetty samalla tavalla uuteen hakemistoon (kansioon) nimeltä "HLS_repo".

Lisää IP-arkisto projektiin siirtymällä IP-luetteloon ja napsauttamalla hiiren kakkospainikkeella "Lisää arkisto …"

Siirry "HLS_repo" -hakemistoosi ja valitse se.

Valinnainen: Luo HLS -videonkäsittelylohko itsellesi!

Vaihe 26: Lisää moduuleja ja IP

Lisää ov7670_axi_stream_capture-, debounce- ja ov7670_controller -moduulit lohkokaavioon napsauttamalla hiiren kakkospainikkeella taustaa ja valitsemalla "Lisää moduuli …"

Lisää samalla tavalla IP -osoitteet:

- HLS_Video_Track

- Videokehyspuskurin kirjoitus

- Videokehyksen puskuri luettu

- Videon ajoitusohjain

- AXI4-Stream videolähtöön

- "Viipale" 3

- Jatkuva

- 2 AXI -ajastimesta

Vaihe 27: IP -määritysasetukset

Kuten kuvissa näkyy

Vaihe 28: Lisää ja määritä PS IP -esto

Lisää ZYNQ7 -prosessointijärjestelmä lohkokaavioon

muokkaa kokoonpanoa:

-

PS-PL-kokoonpano

-

HP

- Ota S HP 0 käyttöön

- Ota S HP käyttöön 1

-

-

Kellon kokoonpano

-

PL Kangaskellot

- FCLK_0 100 MHz: llä

- FCLK_1 25 MHz: llä (OutputClock)

- FLCK_2 35 MHz: llä (<= 50 MHz) (CameraClock)

-

Vaihe 29: Osa 1. PWM -moduulin rakentaminen servomoottoreille

Tuo axi_timer_0 pwm0 uuteen lähtöporttiin pwm_Xaxis

Tuo axi_timer_1 pwm0 uuteen lähtöporttiin pwm_Zaxis

Vaihe 30: Videotulon sivuliitännät (korostettu)

Liitä videotulopuolen IP -lohkot oikein

(* nämä yhteydet on luotava valitsemalla oikeat vaihtoehdot yhteysautomaation aikana) "aclk" axi_stream_capture -ohjelmasta menee osoitteeseen:

- ap_clk videokehyksen puskurin kirjoitus

- ap_clk HLS -videovirran käsittelylohkossa

- *Aclk on AXI smartconnect IP from Video Frame Buffer Kirjoita S_AXI_HP0

- *Aclk, joka vastaa AXI Interconnect IP: n kanavia HLS -videokäsittelylohkon S_AXI -kanaville ja videokehyspuskurille, kirjoita S_AXI_HP0_ACLK PS -lohkoon

Videovirran signaali on yksinkertaisesti kytketty sarjaan kaappauslohkosta Zynq -muistiliitäntään.

- Video siirtyy sieppauslohkosta HLS -käsittelylohkoon.

- Käsitelty video HLS -lohkosta menee kehyspuskurin kirjoituslohkoon.

- *Kehyspuskurin kirjoituslohko muodostaa yhteyden Zynq PS -lohkon HP0 -liittymään.

- Tallennuslohkon lähdöstä tuleva m_axis_tuser -signaali on manuaalisesti kytketty sekä HLS -käsittelylohkon video_in_TUSER -tulosignaaliin että saman lohkon ap_start -signaaliin.

AXI -videovirtaprotokolla käyttää TUSER (tuser) -signaalia osoittamaan videon kehyksen alun AP_Start käskee HLS -lohkon aloittamaan käsittelyn. Kun kytket yksittäisen väylän signaalin ja jaat sen pois tällä tavalla, se on liitettävä myös muun väylän normaaliin päätepisteeseen. Vivado olettaa, että jos liität signaalin manuaalisesti, haluat katkaista yhteyden siihen, mihin se normaalisti muodostaisi yhteyden.

IP -lohkojen kokoonpanoasetukset:

Videokehyksen puskuri kirjoittaa:

Videoformaatit: RGB8

1 näyte kelloa kohti Sarakkeiden enimmäismäärä: 1280 (> = 640) Rivien enimmäismäärä: 960 (> = 480) Suurin tiedon leveys: 8

Vaihe 31: Yhteydet OV7670: een

Lohkossa ov7670_axi_stream_capture

- Tee kaikki tulot ulkoisiksi (napsauta hiiren kakkospainikkeella ja valitse valikosta tai napsauta vasenta painiketta-> ctrl+T)

- Jätä nimet sellaisiksi kuin ne ovat

Ov7670_controller -lohkossa

- Tee kaikki lohkolähdöt ulkoisiksi

- Nimeä config_finished -portti uudelleen led0: ksi

- liitä clk CameraClockiin (<= 50 MHz) (FCLK_2)

Palautuslohkossa

- liitä button1 -tulo ulkoiseen tuloporttiin nimeltä btn0

- liitä out1 ov7670_controller -IP -lohkon uudelleenlähetyslinjaan

- liitä button2 -tulo ulkoiseen tuloporttiin nimeltä btn3

- liitä out2n videon sieppauskellon verkkotunnuksen prosessorin järjestelmän nollaus -IP: n ext_reset_in -tuloon. (*Tämä on ehkä tehtävä IP -osoitteen luomisen jälkeen*)

- liitä clk CameraClockiin (<= 50 MHz) (FCLK_2)

Vaihe 32: Liitännät videolähtöpuolella

Liitännät lohkoille Video Timing Controller (VTC), AXI4-Stream to Video Out ja viipaleet

- Käytä 25 MHz: n kelloa (FCLK_1) vid_io_out_clk ja VTC clk

- Käytä 100 MHz: n kelloa (FCLK_0) AXI4-Stream-videolähtöön

- vtiming_out kohteeseen vtiming_in

- Videokehyksen puskuri Lue m_axis_video menee AXI4-Stream-videolähtöön video_in

- vtg_ce menee gen_clkeniin

- Tie VTC clken, aclken, vid_io_out_ce to Constant dout [0: 0]

- Vie vid_hsync ja vid_vsync ulos ulkoisiin lähtöportteihin vga_hs ja vga_vs. (ei kuvassa)

Viipaleet:

-

Viipaleet on asetettava liitteenä olevien kuvien mukaisesti

- nimeä lohkot uudelleen viipaleiksi, viipalevihreäksi ja viipaleeksi

- asetusten viipalealueet, kuten kuvissa näkyy lohkon nimen mukaan

- liitä jokainen lohkolähtö ulkoiseen porttilähtöön kuvan osoittamalla tavalla.

- vid_data [23: 0] muodostaa yhteyden kunkin viipaleen tuloihin (Din [23: 0])

Vaihe 33: Suorita lohko- ja yhteysautomaatio

Suorita Block Automation yhdistääksesi asiat ZYNQ7 PS -lohkosta. Kuten kuvassa näkyy.

Suorita Yhteys -automaatio luodaksesi kaikki yhteenliittämisen IP -osoitteet. Kiinnitä erityistä huomiota jokaisen kuvan kaikkiin vaihtoehtoihin.

Yhdistä palautuslohkossa out2n videotallennuskellon toimialueen prosessorin järjestelmän nollaus ext_reset_in -tuloon.

Vaihe 34: Luo HDL -kääre

Luo HDL -kääre lohkon suunnitteluun.

Aseta se ylemmäksi moduuliksi.

Vaihe 35: Luo bittivirta, vie laitteisto SDK: hon, käynnistä SDK Vivadosta

Muista sisällyttää bittivirta vientiin.

Bittivirran luominen voi kestää hyvin kauan.

Käynnistä sitten SDK

Vaihe 36: SDK (ei FreeRTOS)

Tämä versio tekee kaiken ilman FreeRTOSia ja tiivistää koodin hienosti.

Luo erillinen BSP laitteiston suunnittelun perusteella. Oletusasetusten pitäisi olla kunnossa. Varmista, että BSP -lähteet on luotu.

Luo sovellus kuvan mukaisesti. (tyhjä sovellus)

Poista automaattisesti luotu pää ja tuo liitetiedostot.

Vaihe 37: FreeRTOS -käyttöönotto

Tämä versio käyttää FreeRTOSia. Luo FreeRTOS901 BSP laitteiston suunnittelun perusteella. Oletusasetusten pitäisi olla kunnossa. Varmista, että BSP -lähteet on luotu.

Luo sovellus kuvan mukaisesti. (tyhjä sovellus)

Poista automaattisesti luotu pää ja tuo liitetiedostot.

Vaihe 38: Käyttöohjeet

Tämä projekti on hieman hankala käynnistää. Seuraa ohjeita järjestyksessä.

Varmista, että ZYBO ei lataa mitään itsestään, kun siihen kytketään virta. Tämä tarkoittaa, että Valmis -LED -valon ei pitäisi syttyä. Yksi tapa tehdä tämä on asettaa käynnistyslähteen hyppääjä asentoon JTAG.

Avaa projekti (FreeRTOS tai ei), jonka haluat ohjelmoida SDK: sta

- Käynnistä ZYBO. Valmis -LED -valon ei pitäisi syttyä.

- Ohjelmoi FPGA bittitiedostolla. Valmis -LED -valon pitäisi syttyä. Led0: n ei pitäisi syttyä.

- Suorita koodi (muista ohittaa aloituspiste, jos teet niin).

Tässä vaiheessa sinun pitäisi saada ulostulo VGA -näyttöön.

Käynnistä uudelleen (jos virheitä tai mitä tahansa): napauta nopeasti PS-SRST-painiketta tai sammuta ZYBO ja kytke se sitten uudelleen päälle. Jatka vaiheesta 2.

Suorittimen pysäyttäminen virheenkorjaimella saa kameran pysymään asennossa liikkumisen sijasta. Videovirta jatkuu joka tapauksessa.

Vaihe 39: Viitteet ja linkit

Xilinx -viiteoppaat ja dokumentaatio:

- PG044 - AXI -Stream videolähtöön

- PG278 - Videokehyspuskuri luku/kirjoitus

Muut linkit:

- Laurin blogi - VDMA -panos

- Laurin blogi - OV7670 - VGA -lähtö BRAM -tekniikan avulla

- Hamsterworks wiki, Mike Fields, OV7670 -koodin alkuperäinen lähde

- Tietolomake, joka näyttää ajoituksen perustiedot

Suositeltava:

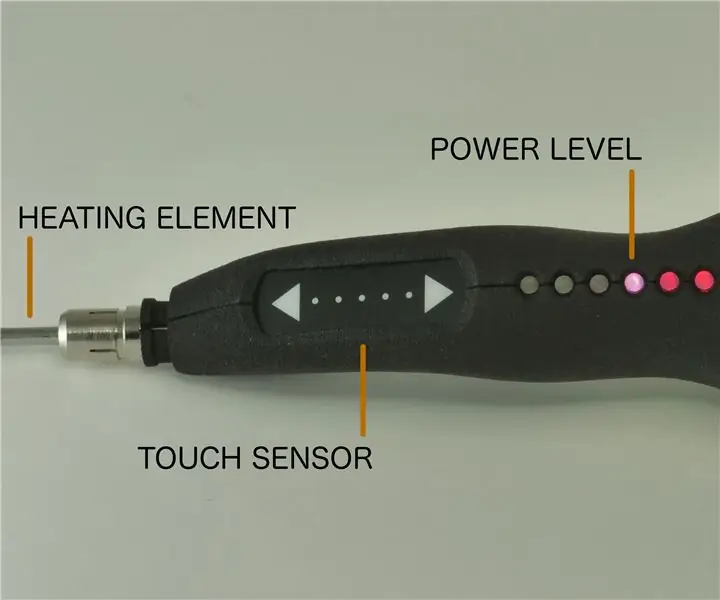

Solderdoodle Plus: Juotosrauda, jossa kosketusohjaus, LED -palaute, 3D -painettu kotelo ja ladattava USB -liitäntä: 5 vaihetta (kuvien kanssa)

Solderdoodle Plus: Juotosrauda, jossa on kosketusohjaus, LED-palaute, 3D-painettu kotelo ja ladattava USB: Napsauta alla käydäksesi Kickstarter-projektisivullamme Solderdoodle Plus -laitteelle, langattomalle ladattavalle kuumalle monitoimityökalulle ja ennakkotilaa tuotantomalli! Https: //www.kickstarter.com/projects/249225636/solderdoodle-plus-cordless-usb-rechargeable-ho

Työpöydän Bluetooth -kaiutin, jossa on äänen visualisointi, kosketuspainikkeet ja NFC: 24 vaihetta (kuvien kanssa)

Työpöydän Bluetooth -kaiutin, jossa on äänen visualisointi, kosketuspainikkeet ja NFC: Hei! Tässä ohjeessa näytän, miten tein tämän työpöydän Bluetooth -kaiuttimen, jossa on hämmästyttävä äänen visualisointi kosketuspainikkeilla ja NFC. Voidaan yhdistää helposti pariksi NFC -yhteensopivien laitteiden kanssa vain napauttamalla. Ei ole fyysistä painiketta

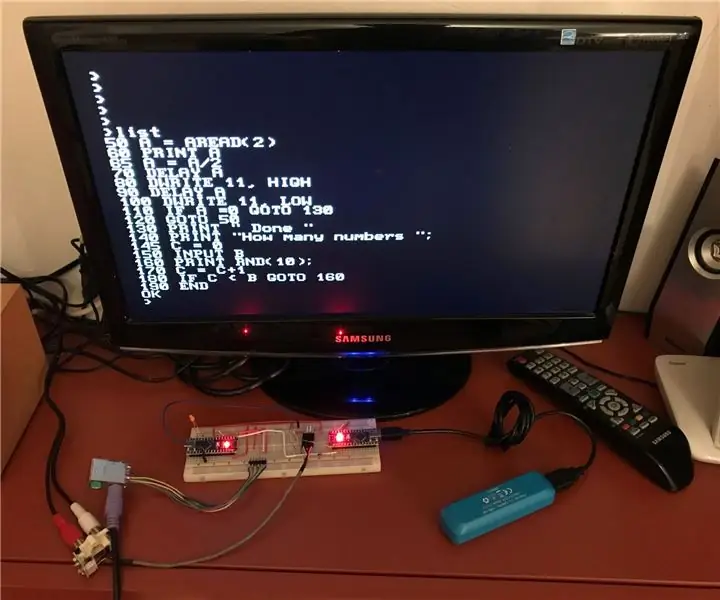

Arduino Basic PC, jossa TV -lähtö: 5 vaihetta (kuvien kanssa)

Arduino Basic PC, jossa TV-lähtö: Tässä oppaassa näytän kuinka rakentaa retro 8-bittinen tietokone, joka käyttää BASICia kahden Arduinon ja muutaman muun komponentin avulla. Voit syöttää muuttujat ja BASIC -ohjelman PS2 -näppäimistöllä, ja lähtö näkyy näytössä, jossa on

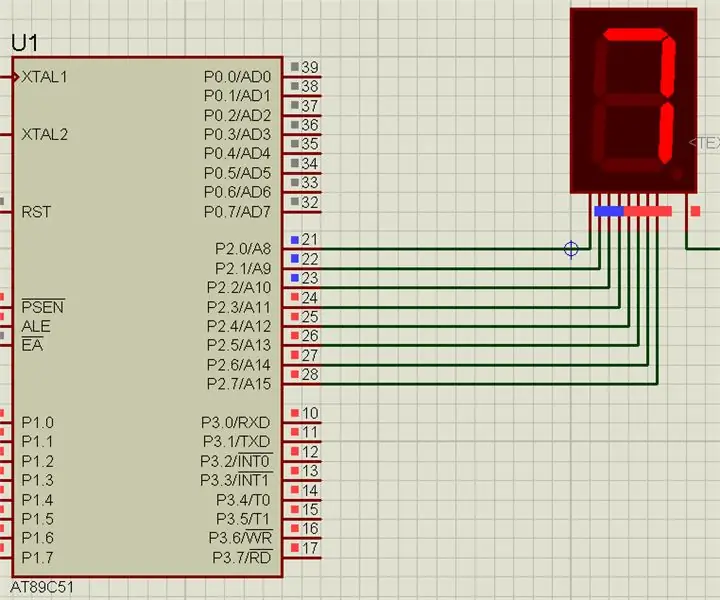

Liitäntä 8051 -mikrokontrolleri, jossa on 7 segmentin näyttö: 5 vaihetta (kuvien kanssa)

Liitäntä 8051 -mikrokontrolleri 7 -segmenttinäytöllä: Tässä projektissa kerromme sinulle, kuinka voimme liittää 7 -segmenttinäytön 8051 -mikrokontrolleriin

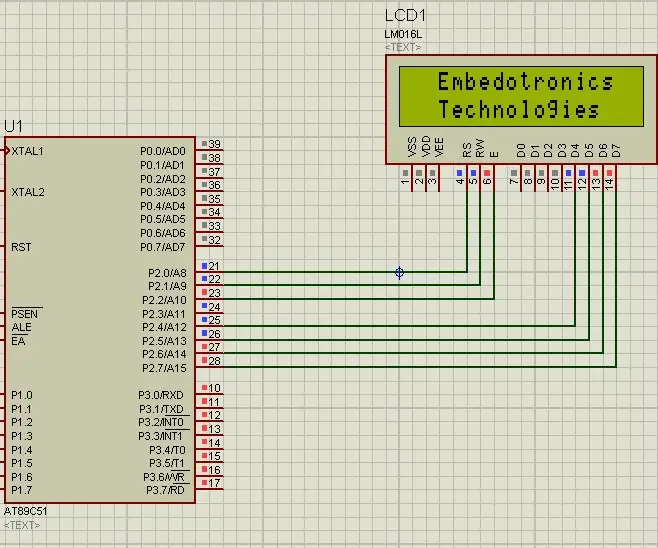

Liitäntä 8051-mikrokontrolleri, jossa LCD-näyttö 4-bittisessä tilassa: 5 vaihetta (kuvien kanssa)

Liitäntä 8051-mikrokontrolleriin, jossa on LCD-näyttö 4-bittisessä tilassa: Tässä opetusohjelmassa kerromme sinulle, kuinka voimme liittää LCD-näytön 8051: n kanssa 4-bittisessä tilassa