Sisällysluettelo:

- Vaihe 1: Lohkokaavio

- Vaihe 2: Toimintaperiaate

- Vaihe 3: Logiikan toteutus

- Vaihe 4: Ratkaise umpikuja

- Vaihe 5: Laitteen määritykset - Matrix0 -piiri

- Vaihe 6: Laitteen määritykset - SPI -kellon logiikka

- Vaihe 7: Laitteen määritykset - Matrix0 -komponenttien ominaisuudet

- Vaihe 8: Laitteen määritykset - Matrix1 -piiri

- Vaihe 9: Laitteen määritykset - 3 -bittinen binäärilaskuri

- Vaihe 10: Laitteen määritykset - 3 -bittinen vertailulogiikka

- Vaihe 11: Laitteen määritykset - Digitaalinen logiikan ja väliaikaisen rekisterin vertailu

- Vaihe 12: Laitteen määritykset - Matrix1 -komponenttien ominaisuudet

- Vaihe 13: Tulokset

- Kirjoittaja John Day day@howwhatproduce.com.

- Public 2024-01-30 09:00.

- Viimeksi muokattu 2025-01-23 14:41.

Ohjausjärjestelmät ja niihin liittyvät laitteet käsittelevät useita virtalähteitä, kuten bias -linjoja tai paristoja, ja niiden on seurattava korkeinta (tai alinta) linjaa tietyn sarjan joukosta.

Esimerkiksi kuormanvaihto usean akun käyttämässä järjestelmässä edellyttää, että järjestelmä valvoo joko minimi- tai maksimijännitettä akkuryhmässä (max tai min tietyn kytkentäalgoritmin funktiona) ja reitittää kuorman dynaamisesti sopivin lähde reaaliajassa. Vaihtoehtoisesti järjestelmä saattaa joutua irrottamaan tilapäisesti pienimmän jännitteen akun liitännän, jotta se latautuu kunnolla.

Toinen esimerkki on nykyaikainen aurinkosähköjärjestelmä, jossa jokainen aurinkopaneeli on varustettu kääntömekanismilla ja aurinkokennolla (jälkimmäinen antaa auringon sijaintitiedot paneelin suuntaamiseksi). Maksimijännitetietojen avulla jokainen aurinkopaneelin sijainti voidaan hienosäätää merkkijonopaneelin perusteella, joka todella tuottaa korkeimman lähtöjännitteen, jolloin saavutetaan ylivoimainen tehon optimointi.

On olemassa useita eri merkkejä kaupallisia IC -laitteita (lähinnä mikro -ohjaimia), jotka voivat periaatteessa toteuttaa maksimijännitteen seuraajan. Ne vaativat kuitenkin ohjelmointia ja ovat vähemmän kustannustehokkaita kuin sekoitussignaaliratkaisu. Dialog GreenPAKTM -suunnittelun täydentäminen voi vaikuttaa myönteisesti suunnittelun kohtuuhintaan, kokoon ja modulaarisuuteen. Tässä suunnittelussa hyödynnetään sekä analogisten että digitaalisten piirien yhdistämisestä yhdeksi siruksi.

Tässä Instructable-ohjelmassa toteutetaan analoginen käyttöliittymä ja digitaalinen logiikka, joka vaaditaan maksimi- (tai lopulta min) jännitehaun toteuttamiseen kahdeksan eri lähteen joukosta.

8-kanavaisen analogisen max/min-jännitemonitorin toteuttamiseen käytetään SLG46620G: tä.

Seuraavassa kuvataan vaiheet, jotka tarvitaan ymmärtämään, miten ratkaisu on ohjelmoitu luomaan 8-kanavainen analoginen max/min-jännitemonitori. Jos haluat vain saada ohjelmoinnin tuloksen, lataa GreenPAK -ohjelmisto nähdäksesi jo valmistuneen GreenPAK -suunnittelutiedoston. Liitä GreenPAK-kehityssarja tietokoneeseesi ja luo ohjelma, jotta voit luoda 8-kanavaisen analogisen max/min-jännitemonitorin.

Vaihe 1: Lohkokaavio

Kuva 1 esittää toteutetun järjestelmän yleiskaaviota.

Jopa kahdeksan vaihtelevan jännitelähteen merkkijono multipleksoidaan ja liitetään GreenPAKin ADC -moduuliin, joka on kytketty mukautettuun sisäiseen rakenteeseen, joka pystyy valitsemaan lähteen, jolla on korkein jännite suhteessa muihin. Sisäinen logiikka lähettää nämä tiedot näyttöä tai jatkokäsittelyä varten.

Suunnittelu perustuu GreenPAK SLG46620G -tuotteeseen, koska se sisältää kaikki sovellukseen tarvittavat analogiset ja digitaaliset rakennuspalikat. Tässä toteutuksessa matriisi skannataan analogisella ADG508 -multiplekserillä, jota ohjaa GreenPAK IC.

Lähtötiedot ovat 3-bittinen digitaalinen numero, joka vastaa jännitelähteen numeroa maksimijännitteellä. Suora tapa saada nämä tiedot on näyttää numero 7-segmenttisellä näytöllä. Se voidaan tehdä helposti liittämällä SLG46620G: n digitaalilähtö 7-segmenttiseen näytönohjaimeen, kuten viitteessä kuvattuun GreenPAK-ratkaisuun tai yleiseen 74LS47-IC: hen.

Esitetty piiri etsii maksimijännitettä. Jotta malli voitaisiin muuttaa minimijännitteen etsijäksi, analogisen multiplekserin ja GreenPAK-analogitulon väliin on lisättävä yksinkertainen esikäsittelypiiri, joka vähentää multiplekserilähdön 1 V: n vertailujännitteestä.

Vaihe 2: Toimintaperiaate

Suunnittelun tavoitteena on valita lähde, jolla on enimmäisjännite, joten skannaus suoritetaan koko ryhmälle samalla kun tallennetaan viimeinen-maks. -Arvo ja verrataan sitä seuraavaan tulon arvoon (joka kuuluu skannauksen seuraavaan jännitelähteeseen).

Seuraavassa viitataan täydelliseen multipleksointisekvenssiin kaikkien tulojen kohdalla "skannauksena" tai "silmukana".

Kahden arvon vertailu ei onnistu ACMP -komponenttien avulla (joka on saatavana SLG46620G: ssä), vaan pikemminkin DCMP -moduulilla, kun arvot on vastaavasti digitoitu. Tämä on kehittynyt ja hienostunut tekniikka, jota käsitellään ensin viitteessä.

Kuva 2 osoittaa, miten SLG46620G on rakennettu tätä mallia varten.

Analoginen tulosignaali siirtyy ADC-tuloon PGA-komponentin kautta, ja Gain-arvo on 1. Erilaisia Gain-asetuksia on myös mahdollista löytää parhaiten sopiviksi etupuolen ilmastointielektroniikan kanssa, joka on omistettu tulojännitteiden kartoittamiselle 0-1 V GreenPAK ADC -moduulin valikoima.

ADC toimii yksipäisessä tilassa ja muuntaa analogisen signaalin 8-bittiseksi digitaaliseksi koodiksi, joka sitten siirretään DCMP-moduuliin. Digitaalinen koodi syötetään myös SPI -lohkoon, joka on konfiguroitu ADC/FSM -puskuriksi, johon digitaalinen koodi voidaan tallentaa eikä muutu, ennen kuin seuraava pulssi tulee SPI CLK -tuloon. Huomaa, että oma logiikkalohko ohjaa SPI CLK -tuloa. Tutkimme tätä osaa myöhemmin, koska tämä on "ydin" -logiikka, joka vastaa asianmukaisesta toiminnasta. Uusi digitaalinen koodi tallennetaan SPI -moduuliin vain, jos se kuuluu todelliseen maksimitulojännitteeseen.

DCMP -komponenttia käytetään nykyisten ADC -tietojen vertaamiseen SPI -lohkoon tallennetun viimeisen voittajan kanssa (eli viimeksi löydetty maksimi). Se tuottaa pulssin OUT+ -ulostulossa, kun uusi ADC -data on suurempi kuin edellinen. Käytämme OUT+ -signaalia päivittääksemme SPI -lohkon uudella voittajalla.

Yleinen kellosignaali ohjaa ADC -konversioita ja yleisiä ajoituksia. Kun muunnos on suoritettu, ADC: n INT -lähtösignaali pulssi, joka on sovitettu yhteen ADC: n rinnakkaisdatan kanssa. Käytämme INT-lähtöä myös 3-bittisen binäärilaskurin lisäämiseen, jonka DFF: t toteuttavat Matrix1: ssä, mikä on hyödyllistä kolmesta syystä:

1. Laskurilähtölinjat osoittavat ulkoista analogista multiplekseriä ja palvelevat siten seuraavaa syöttöjännitettä ADC: lle;

2. Laskenta jäädytetään 3-bittiseen rekisteriin (toteutettu Matrix1: ssä) väliaikaisen voittajan tallentamiseksi skannauksen aikana;

3. Laskenta dekoodataan päivittämään toinen 3-bittinen rekisteri (toteutettu Matrix0: ssa), kun skannaus on valmis.

Vaihe 3: Logiikan toteutus

ADC -moduuli tarjoaa peräkkäin kaikkien tulojännitteiden muunnetut tiedot peräkkäin loputtomiin. Kun multiplekserille on osoitettu 0b111 (desimaali 7), laskuri siirtyy 0b000: een (desimaali 0), jolloin aloitetaan uusi tulojännitteiden skannaus.

Skannauksen aikana ADC INT -lähtösignaali generoidaan, kun rinnakkainen datalähtö on kelvollinen. Kun tämä signaali pulssi, analogisen multiplekserin on vaihdettava seuraavaan tuloon, jolloin PGA saa vastaavan jännitteen. Siksi ADC INT -lähtö on kuvion 2 3-bittisen binäärilaskurin suora kellosignaali, jonka 3-bittinen rinnakkaislähtösana osoittaa suoraan ulkoista analogista multiplekseriä (“V select” kuviossa 1).

Viitataan nyt esimerkkiin, jossa tulojännitteillä oletetaan olevan seuraavat suhteet:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

Kuvio 3 edustaa tärkeimpiä signaaleja, jotka liittyvät max-päätösmekanismiin.

Koska tiedot lopulta kellotetaan SPI -puskurirekisteriin synkronisesti INT -pulssien kanssa, on olemassa vertailuikkuna, jossa SPI -puskurin sisältöä verrataan seuraavaan ADC -muunnostulokseen. Tämä erityinen ajoitus johtaa OUT+ -pulssien muodostamiseen DCMP -lähdössä. Voimme hyödyntää näitä pulsseja uusien arvojen lataamiseen SPI -puskurirekisteriin.

Kuten edellisen kuvan SPI -puskuritietoriviltä käy ilmi, SPI -rekisteri sisältää aina aika ajoin suurimman arvon kahdeksan tulon joukosta, ja se päivitetään vasta, kun DCMP -moduuli havaitsee suuremman arvon (viitaten DCMP: hen) OUT+ tulostuslinja, puuttuvat pulssit aiheuttavat sen, että V2 pysyy lukittuna rekisterissä, kunnes sitä verrataan V5: een).

Vaihe 4: Ratkaise umpikuja

Jos toteutettu logiikka olisi aivan kuten edellä kuvattu, on selvää, että törmäisimme umpikujaan: järjestelmä pystyy havaitsemaan vain korkeammat jännitteet kuin SPI -puskurirekisteriin tallennetut jännitteet.

Tämä pätee myös siinä tapauksessa, että tämä jännite laskee ja toinen tulo, joka on toistaiseksi sitä pienempi, tulee korkeimmaksi: sitä ei koskaan havaita. Tämä tilanne selitetään paremmin kuviossa 4, jossa on vain 3 tulojännitettä. selkeys.

Iteraation 2 aikana V3 putoaa ja V1 on todellinen maksimijännite. DCMP -moduuli ei kuitenkaan tarjoa pulssia, koska SPI -puskurirekisteriin tallennettu data (vastaa 0,6 V) on suurempi kuin V1 (0,4 V).

Järjestelmä toimii tällöin "absoluuttisena" enimmäishakijana eikä päivitä lähtöä oikein.

Hyvä tapa ratkaista tämä ongelma on pakottaa tietojen lataaminen uudelleen SPI -puskurirekisteriin, kun järjestelmä suorittaa kaikkien kanavien täydellisen pollausjakson.

Itse asiassa, jos jännite kyseisessä tulossa on edelleen korkein, mikään ei muutu ja ohjaus jatkuu turvallisesti (yllä olevaan kuvaan 4 viitaten, tämä on silmukkakertoimet 0 ja 1). Toisaalta, jos jännite kyseisessä tulossa laskee sattumalta arvoon, joka on pienempi kuin toinen tulo, arvon uudelleenlataaminen antaa DCMP -moduulille mahdollisuuden tuottaa OUT+ -pulssi, kun verrataan sitä uuteen maksimiarvoon (tämä on silmukan toistojen 2 ja 3 tapauksessa).

Logiikkapiiri on tarpeen ongelman ratkaisemiseksi. Sen on luotava kellosignaali SPI-komponentille, kun silmukka saavuttaa todellisen maksimitulon, mikä pakottaa sen päivitetyn datasanan lataamisen uudelleen SPI-puskurirekisteriin. Tätä käsitellään jäljempänä kohdissa 7.2 ja 7.6.

Vaihe 5: Laitteen määritykset - Matrix0 -piiri

SLG46620G -laitteessa on kaksi matriisilohkoa, kuten kuviossa 2 on esitetty. Seuraavat kuvat esittävät vastaavat laitekokoonpanot.

Piirin yläosa on "silmukkarekisteri", joka toteutetaan kolmella DFF: llä (DFF0, DFF1 ja DFF2). Tulon multiplekserin jokaisen silmukan jälkeen päivitetään 7-segmenttiselle näyttöohjaimelle "voittajan" binääriluku, eli tulo, jolla on korkein jännite viimeisessä skannauksessa. Sekä kello DFF -laitteille että tiedot tulevat Matrix1: ssä toteutetusta logiikasta portin P12, P13, P14 ja P15 kautta.

Alaosa on analoginen etupää, jonka tulo on nastassa 8 ja PGA vahvistuksella x1. ADC INT -lähtö menee sekä SPI: n kellon logiikkaan että matriisiin 1 portin P0 kautta, missä se toimii kellosignaalina toteutetulle laskimelle.

Rinnakkaiset ADC- ja SPI -datalähdöt on merkitty NET11- ja NET15 -merkinnöillä, jotka liitetään Matrix1: n DCMP -komponenttiin.

Vaihe 6: Laitteen määritykset - SPI -kellon logiikka

Kuten edellä "Logiikan toteutus" -osiossa todettiin, SPI -puskurirekisteri päivitetään aina, kun todellisen tallennetun arvon ja uuden ADC -muuntotiedon vertailu tuottaa pulssin DCMP OUT+ -ulostulossa.

Signaalin eheys varmistetaan, jos tämä signaali on AND-ed ADC INT -lähdön kanssa. Tämä välttää piikin ja väärän laukaisun.

Olemme myös korostaneet, että umpikujatilanteiden ohittamiseksi SPI -puskuri on päivitettävä, kun silmukka saavuttaa todelliset voittajatiedot.

Pelissä on kolme signaalia oikean SPI -kellon aikaansaamiseksi:

1. ADC INT -lähtö (LUT0-IN1)

2. DCMP OUT+ -lähtö (LUT0-IN0 portin P10 kautta)

3. Määrä vastaa salpasignaalia (LUT0-IN2 portin P11 kautta)

Kaksi ensimmäistä ovat AND-ed ja molemmat OR-ed. Jälkimmäisen kanssa LUT0: ssa, jonka toteutus on määritetty kuten kuvassa 6.

Vaihe 7: Laitteen määritykset - Matrix0 -komponenttien ominaisuudet

Kuvioissa 7-10 esitetään Matrix0: lle kuuluvat muut komponenttien ominaisuusikkunat.

Vaihe 8: Laitteen määritykset - Matrix1 -piiri

Vaihe 9: Laitteen määritykset - 3 -bittinen binäärilaskuri

Piirin yläosa sisältää logiikkaelementtejä, lähinnä 3-bittisen binäärisen laskurin, jonka kellonaika on ADC INT -lähtö, kuten jo keskusteltiin. Tämä laskuri on toteutettu melko "vakio" -kaavion avulla, joka on esitetty kuvassa 12.

Tämä laskuri toteutetaan suunnittelussamme varvastossujen DFF9, DFF10, DFF11 ja INV1, LUT4, LUT8 avulla. DFF9 -lähtö on LSB, kun taas DFF11 on MSB, kuten kuvassa 13 on esitetty.

LUT4 on määritetty XOR: ksi, kun taas LUT8 suorittaa kuvion 12 AND-XOR-logiikan.

Laskurilähdöt menevät kolmeen digitaaliseen ulostulonastaan ulkoisen analogisen multiplekserin osoittamiseksi.

LUT10 dekoodaa laskurin koodin, kun skannaus on valmis, ja syöttää pulssin Matrix0: lle DLY8: n ja portin P12 kautta. Tämä yksinkertaisesti saavutetaan AND-laskemalla laskurin lähdöt, dekoodaamalla numero 7 dec (0b111 binääri, silmukan loppu).

Vaihe 10: Laitteen määritykset - 3 -bittinen vertailulogiikka

Kuva 15 esittää piiriä, jota käytetään havaitsemaan, milloin silmukka iteroi nykyisellä "voittaja" -osoitteella. Tässä tapauksessa, kuten jo keskusteltiin, digitaalisen pulssin pitäisi pakottaa nykyisen ADC-tuloksen uudelleenlataus mahdollisen umpikujan ratkaisemiseksi.

"Voittaja" -osoite tallennetaan Matrix1: n väliaikaiseen rekisteriin (katso alla), kun taas nykyinen osoite lähetetään binäärilaskurilla.

XNOR -portit tarjoavat todellisen (logiikka 1 tai "korkea") lähdön, kun molemmat tulot ovat yhtä suuret. Tämän signaalin antaminen kaikille biteille (LUT9) antaa meille pulssin, kun molemmat binaarikoodit ovat samat. Lisätietoja XOR -porteista pariteettitarkistajana on viitteessä.

"Counter-equals-Latch" -signaali välitetään Matrix0: lle portin P11 kautta.

Vaihe 11: Laitteen määritykset - Digitaalinen logiikan ja väliaikaisen rekisterin vertailu

Kuvan 11 alaosassa (korostettu kuvassa 16) näkyy DCMP-lohko, tämän suunnittelun päätöksenteko-osa.

DFF6, 7 ja 8 muodostavat 3-bittisen rekisterin väliaikaisen tulonumeron "voittaja" tallentamiseksi silmukan ollessa käynnissä. Flip-Flops-tulo on 3-bittinen binäärinen laskuriulostulo, kuten näkyy kuvion 11 globaalissa Matrix1-piirissä, tässä ohitettuna selvyyden vuoksi.

Tämän rekisterin lähdöt eivät voi ohjata suoraan 7-segmenttistä näyttöä, koska tähän tallennettu arvo muuttuu skannauksen aikana ja sitä tulisi pitää”kelvollisena” vasta itse skannauksen lopussa.

Tästä syystä väliaikaiset rekisterilähdöt muodostavat yhteyden Matrix0: n silmukkarekisteriin matriisien välisten porttien P13, P14 ja P15 kautta.

On tärkeää huomata kuvassa 16, että väliaikainen rekisteri kellotetaan DCMP OUT+ -ulostulolla, kun ADC-SPI-rekistereiden vertailussa saadaan uusi maksimi.

Sama OUT+ -signaali välitetään Matrix0: lle, SPI CLK Logic, portin P10 kautta.

Vaihe 12: Laitteen määritykset - Matrix1 -komponenttien ominaisuudet

Kuvissa 17-19 on esitetty Matrix1: n komponenttiominaisuusikkunat.

Vaihe 13: Tulokset

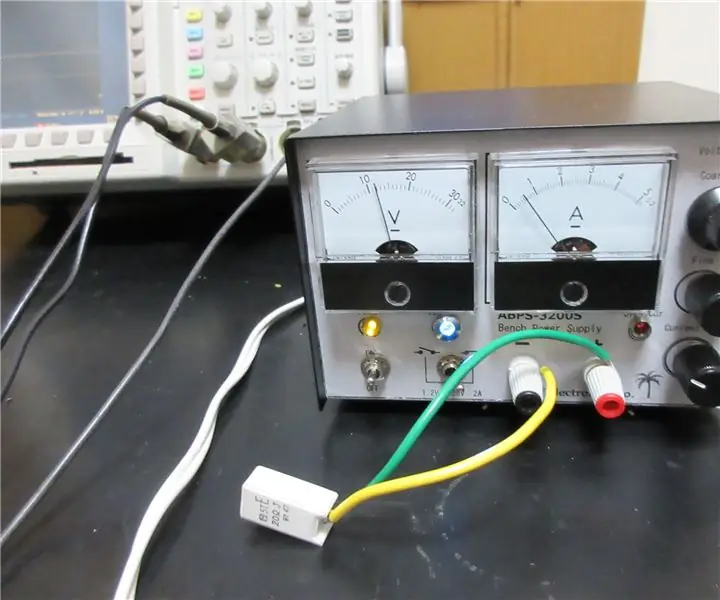

Toteutuksen testaamiseksi on rakennettu arviointikortin prototyyppi, jossa 8 analogista tulojännitettä saadaan sarjasta vastuksenjakajia, joissa on TrimPots (kuten kuvassa 20).

Käytetty multiplekseri on ADG508, osa, joka voi toimia yhdellä virtalähteellä (12 V).

7-segmenttinen näytönohjain on 74LS47. Se purkaa rinnakkaissyöttösanan ja ohjaa suoraan 7-segmenttisen yhteisen anodin näyttöä.

Arviointitaulussa on 2x10-kulmaliitin, joka voidaan liittää suoraan GreenPAK Advanced Development Platformiin laajennusliittimessään, kuten kuvassa 21 on esitetty.

Yhdessä GreenPAK Advanced Development Platformin kanssa on erittäin helppoa mitata signaaleja nopeaa tarkistusta varten. Esimerkiksi kuvassa 22 esitetään joukko signaaleja (vastaavasti CLOCK, ADC INT -lähtö ja DCMP OUT+ -lähtö) HP 54620A Logic Analyzer -laitteella. Aaltomuodot laukaistaan OUT+ -signaalin nousevasta reunasta (laajuudessa, joka on merkitty "A> B"), joten tämä on aaltomuodon sieppaus, kun analogitulojen välillä havaitaan uusi maksimijännite. Itse asiassa se saatiin pyörittämällä yhtä arviointikortin TrimPot -pisteistä kuvassa 22 esitetyn vastaavan jännitteen lisäämiseksi.

Kuva 23 esittää arviointikomitean kaaviota.

Johtopäätös

Tässä Instructable-ohjelmassa toteutimme kahdeksan kanavan maksimijännitteen (tai min) etsimen, jota käytetään yleisenä lisäyksenä monikanavaisiin ohjausjärjestelmiin. Esitetty lähestymistapa hyödyntää GreenPAK -komponenttien kehittyneitä ominaisuuksia ja näyttää, kuinka on mahdollista integroida yhteen siruun analogiset ja digitaaliset toiminnot. Useat kaupalliset IC: t voidaan korvata Dialog GreenPAK -laitteilla, jotta sovelluksen kokoa ja kustannuksia voidaan pienentää.

Suositeltava:

LEDura - analoginen LED -kello: 12 vaihetta (kuvilla)

LEDura - Analoginen LED -kello: Pitkän aikaa vain erilaisten projektien tekemisen jälkeen päätin tehdä ohjattavan itse. Ensimmäiseksi opastan sinua prosessissa, jolla voit tehdä oman analogisen kellosi, joka on valmistettu mahtavalla osoitettavalla LED -renkaalla. Sisärengas näyttää tunnit, ou

Kuinka tehdä analoginen kello ja digitaalikello led -nauhalla Arduinon avulla: 3 vaihetta

Kuinka tehdä analoginen kello ja digitaalikello led -nauhalla Arduinon avulla: Tänään teemme analogisen kellon & Digitaalinen kello, jossa on Led Strip ja MAX7219 Dot -moduuli Arduinolla.Se korjaa ajan paikallisen aikavyöhykkeen mukaan. Analoginen kello voi käyttää pidempää LED -nauhaa, joten se voidaan ripustaa seinälle taideteokseksi

DIY -analoginen soitin USB -näppäimistöön: 4 vaihetta

DIY Analog Dialer to USB Keyboard: Tein tämän projektin huvin vuoksi, mutta tämä asia toimii normaalina näppäimistönä kaiken kanssa

DIY analoginen muuttuva penkki virtalähde W/ tarkkuusvirran rajoitin: 8 vaihetta (kuvilla)

DIY -analoginen muuttuva penkki -virtalähde W/ tarkkuuden virranrajoitin: Tässä projektissa näytän sinulle, kuinka käyttää kuuluisaa LM317T: tä virran tehostransistorilla ja kuinka käyttää lineaaritekniikan LT6106 -virtavahvistinta tarkan virran rajoittimelle. voit käyttää jopa yli 5A

Arduino DIY analoginen lämpömittari: 7 vaihetta (kuvilla)

Arduino DIY analoginen lämpömittari: Rakkaat ystävät, tervetuloa toiseen opetusohjelmaan! Tänään opimme käyttämään tätä analogista voltimittaria Arduinon kanssa ja saamaan sen näyttämään lämpötilan jännitteen sijasta. Kuten näette, tässä muunnetussa volttimittarissa voimme nähdä lämpötilan