Sisällysluettelo:

- Vaihe 1: Mikä on Vivado HLS?

- Vaihe 2: HLS -videokirjasto

- Vaihe 3: Syntetisointi

- Vaihe 4: Versiointi ja muut tiedot vientiä varten

- Vaihe 5: Vienti Vivado IP -kirjastoon

- Vaihe 6: Synteesi ja vienti -analyysi

- Vaihe 7: IP -kirjaston lisääminen Vivadoon

- Vaihe 8: Päivityksen tekeminen

- Vaihe 9: Lisätietoja ja tietoja

- Vaihe 10: Lähtö ja tulo

- Vaihe 11: AXI -rekisterin liitäntä

- Vaihe 12: Dataflow Pragma

- Kirjoittaja John Day day@howwhatproduce.com.

- Public 2024-01-30 09:03.

- Viimeksi muokattu 2025-01-23 14:44.

Oletko koskaan halunnut käsitellä videota reaaliajassa lisäämättä paljon latenssia tai sulautetussa järjestelmässä? FPGA: ita (Field Programmable Gate Arrays) käytetään joskus tähän; videonkäsittelyalgoritmien kirjoittaminen laitteistomäärityskielillä, kuten VHDL tai Verilog, on kuitenkin parhaimmillaan turhauttavaa. Anna Vivado HLS, Xilinx -työkalu, jonka avulla voit ohjelmoida C ++ -ympäristössä ja luoda siitä laitteistomääritysten kielikoodin.

Tarvittavat ohjelmistot:

- Vivado HLS

- Vivado

- (Jos käytät AXI -rekistereitä) Vivado SDK

(Valinnainen) Lataa Xilinxin tekemät esimerkit täältä:

Esimerkkejä Xilinx HLS -videoista

Vaihe 1: Mikä on Vivado HLS?

Vivado HLS on työkalu, jolla c ++: n kaltainen koodi muutetaan laitteistorakenteiksi, jotka voidaan toteuttaa FPGA: lla. käytettäväksi Vivadon kanssa.

Lataa liitetiedostot ja aseta ne lähelle projektin luomista. (nimeä ne takaisin "top.cpp" ja "top.h", jos niillä on satunnaistettu nimi)

Vaihe 2: HLS -videokirjasto

HLS -videokirjastossa on tässä asiakirjassa viitteellisiä asiakirjoja: XAPP1167 Toinen hyvä resurssi on Xilinx Wiki -sivu.

Käynnistä Vivado HLS.

Luo uusi projekti.

Ota edellisessä vaiheessa lataamasi tiedostot ja lisää ne lähdetiedostoiksi. (Huomaa: tiedostoja ei kopioida projektiin, vaan ne pysyvät siellä missä ne ovat)

Valitse sitten ylätoiminto Selaa -painikkeella.

Valitse seuraavalla sivulla käyttämäsi Xilinx -osa.

Vaihe 3: Syntetisointi

Ratkaisu => Suorita C -synteesi => Aktiivinen ratkaisu

~ 227,218 sekunnin kuluttua se on tehtävä. (Huomaa: todellinen synteesiaikasi vaihtelee monien tekijöiden perusteella)

Vaihe 4: Versiointi ja muut tiedot vientiä varten

Versionumerot ovat vuorovaikutuksessa Vivadon kanssa, jolloin voit päivittää mallin IP -osoitteen. Jos kyseessä on vähäinen version muutos, se voidaan tehdä, kun suuret versiomuutokset edellyttävät uuden lohkon manuaalista lisäämistä ja vanhan poistamista. Jos käyttöliittymänne eivät ole muuttuneet ja versiopäivitys on vähäinen, päivitys voidaan tehdään automaattisesti automaattisesti painamalla IP -päivitys -painiketta. Voit ajaa "report_ip_status" Vivado tcl -konsolissa nähdäksesi IP -osoitteesi tilan.

Aseta versionumerot ja muut tiedot kohdasta Ratkaisu => Ratkaisuasetukset…

Vaihtoehtoisesti nämä asetukset voidaan määrittää viennin aikana.

Vaihe 5: Vienti Vivado IP -kirjastoon

Ratkaisu => Vie RTL

Jos et määrittänyt IP -kirjaston tietoja edellisessä vaiheessa, voit tehdä sen nyt.

Vaihe 6: Synteesi ja vienti -analyysi

Tällä näytöllä näemme vientimoduulimme tilastot, jotka osoittavat, että se täyttää kellon ajan 10ns (100MHz) ja kuinka paljon kustakin resurssista se käyttää.

Tämän, yhteenvetoraporttimme ja datavirta -analyysimme yhdistelmän avulla voimme nähdä, että se kestää 317338 kellojaksoa * 10ns kellojakso * 14 putkilinjan vaihetta = 0,04442732 sekuntia. Tämä tarkoittaa sitä, että kuvankäsittelymme lisäämä kokonaisviive on alle kahdeskymmenesosa sekunnista (kun kellotaajuus on 100 MHz).

Vaihe 7: IP -kirjaston lisääminen Vivadoon

Jotta voit käyttää syntetisoitua IP -lohkoa, sinun on lisättävä se Vivadoon.

Lisää Vivadossa projektisi IP-arkisto siirtymällä IP-luetteloon ja napsauttamalla hiiren kakkospainikkeella "Lisää arkisto …"

Siirry Vivado HLS -projektihakemistoosi ja valitse ratkaisuhakemisto.

Sen pitäisi ilmoittaa löytämänsä IP.

Vaihe 8: Päivityksen tekeminen

Joskus sinun on tehtävä muutoksia HLS -lohkoosi sen jälkeen, kun olet sisällyttänyt sen Vivado -suunnitteluun.

Voit tehdä tämän tekemällä muutokset ja uudelleensyntetisoimalla ja viemällä IP -osoitteen korkeammalla versionumerolla (katso yksityiskohdat edellisessä vaiheessa tärkeiden/vähäisten versioiden muutoksista).

Kun olet muuttanut uuden version vientiä, päivitä IP -tietovarastosi Vivadossa. Tämä voidaan tehdä joko silloin, kun Vivado huomaa, että IP -osoite on muuttunut arkistossa, tai aktivoitava manuaalisesti. (Huomaa, jos päivität IP -tietovarastosi aloittamisen jälkeen, mutta ennen kuin vienti on valmis HLS: ssä, IP -osoite ei ole tilapäisesti siellä, odota sen päättymistä ja päivitä uudelleen.)

Tässä vaiheessa pitäisi ilmestyä ikkuna, jossa on tiedot siitä, että IP -levyä on muutettu levyllä, ja antaa sinulle mahdollisuuden päivittää se "Päivitä valitut" -painikkeella. Jos muutos oli vähäinen version muutos eikä mikään käyttöliittymä muuttunut, sen jälkeen tämän painikkeen painaminen korvaa automaattisesti vanhan IP -osoitteen uudella, muuten työ voi vaatia enemmän työtä.

Vaihe 9: Lisätietoja ja tietoja

Seuraavat vaiheet tarjoavat lisätietoja siitä, miten HLS -synteesi toimii ja mitä voit tehdä sen kanssa.

Esimerkki projektista, jossa käytetään HLS -syntetisoitua IP -lohkoa, on tässä ohjeessa.

Vaihe 10: Lähtö ja tulo

Lopullisen IP -lohkon lähdöt ja tulot määritetään analyysistä, jonka syntetisaattori tekee datavirrasta ylä- ja ulos -toiminnosta.

Kuten VHDL: ssä tai verilogissa, HLS: n avulla voit määrittää IP -yhteyksien tiedot. Nämä rivit ovat esimerkkejä tästä:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE -akselin portti = video_in nippu = INPUT_STREAM #pragma HLS INTERFACE -akselin portti = video_out -nippu = OUTPUT_STREAM #pragma HLS INTERFACE s_axilite port = x nippu = CONTROL_BUS offset = 0x14 #pragma h_xbite

Näet, kuinka nämä direktiivit vaikuttavat IP -lohkossa näytettyihin portteihin.

Vaihe 11: AXI -rekisterin liitäntä

Saadaksesi tulon/lähdön IP -lohkostasi PS: lle/siitä, hyvä tapa tehdä tämä on AXI -liitännän kautta.

Voit määrittää tämän HLS -koodissasi, mukaan lukien siirtymät, joita käytetään arvon käyttämiseen myöhemmin seuraavasti:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE s_axilite port = x nippu = CONTROL_BUS offset = 0x14

#pragma HLS INTERFACE s_axilite port = y nippu = CONTROL_BUS offset = 0x1C #pragma HLS dataflow

x = 42;

y = 0xDEADBEEF; }

Kun yhteys on muodostettu oikein Vivadossa, voit käyttää arvoja käyttämällä tätä koodia Vivado SDK: ssa:

#include "parametrit.h"

#define xregoff 0x14 #define yregoff 0x1c x = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+xregoff); y = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+yregoff);

Tämä johtaa siihen, että x: ssä on 42 ja y: ssä 0xdeadbeef

Vaihe 12: Dataflow Pragma

#Pragma DATAFLOW: n sisällä tapa, jolla koodi toteutetaan, muuttuu normaalista C ++: sta. Koodi on yhdistetty niin, että kaikki ohjeet ovat aina käynnissä datan eri osissa (ajattele sitä kuin tehtaan kokoonpanolinjaa, jokainen asema tekee jatkuvasti yhtä toimintoa ja välittää sen seuraavalle asemalle)

kuvasta näet, että jokainen direktiivi

Huolimatta siitä, että ne näyttävät olevan normaaleja muuttujia, img -objektit toteutetaan itse asiassa pieninä puskureina komentojen välillä. Kuvan käyttäminen toiminnon tulona "kuluttaa" sen eikä tee sitä enää käyttökelpoiseksi. (Siksi kaksoiskappaleiden tarve)

Suositeltava:

MIDI-ohjattu askelmoottori, jossa on suora digitaalinen synteesi (DDS) -piiri: 3 vaihetta

MIDI-ohjattu askelmoottori, jossa on suora digitaalinen synteesi (DDS) -piiri: Onko sinulla koskaan ollut aavistusta, että sinun täytyi muuttua miniprojektiksi? No, pelasin luonnoksella, jonka olin tehnyt Arduino Due: lle ja jonka tarkoituksena oli tehdä musiikkia AD9833 Direct Digital Synthesis (DDS) -moduulilla … ja jossain vaiheessa ajattelin & q

Phono -Chronoxyle - 360 asteen synteesi: 3 vaihetta (kuvilla)

Phono -Chronoxyle - 360 asteen synteesi: Julien Signoletin kuvanveistäjä Pariisista ja muusikko Mathias Durand lähestyi minua interaktiivisen ääniinstallaation järjestämiseksi Parc Floralissa Pariisissa Nuit Blanche 2019 -tapahtumaan. Asennus olisi ulkona, enkä olisi läsnä aikana sisään

Sikarilaatikon synteesi: 14 vaihetta (kuvilla)

Cigar Box Synth: Tässä on uusin syntetisaattorini, joka on valmistettu ajastimista 555 ja 556 sekä 4017 ic. Muutama kuukausi sitten tällainen rakentaminen olisi ollut taitotasoni ulkopuolella. Viime kuukausien aikana olen kuitenkin koonnut yksinkertaisia syntetisaattoreita saadakseni paremman

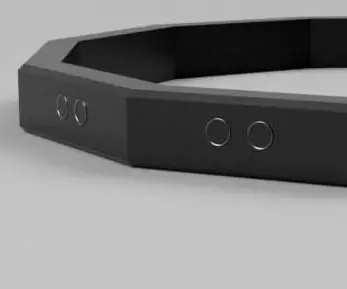

IOT123 - D1M BLOCK - 2xAMUX -kokoonpano: 7 vaihetta (kuvilla)

IOT123 - D1M BLOCK - 2xAMUX -kokoonpano: D1M BLOCKS lisää kosketuslaukkuja, tarroja, napaisuusoppaita ja läpivientejä suosittuihin Wemos D1 Mini SOC/Shields/Clones -laitteisiin. Yksi ESP8266 -sirun ongelmista on, että siinä on vain yksi analoginen IO -nasta. Tämä opas näyttää kuinka 2xA kootaan

Vivado Simluationin käyttö: 6 vaihetta

Kuinka käyttää Vivado Simluation: Olen tehnyt tämän simulaatioprojektin verkkotunnille. Projektin on kirjoittanut Verilog. Käytämme simulointia Vivadossa visualisoidaksemme aaltomuodon enable_sr (mahdollinen numero) aiemmin luodusta sekuntikelloprojektista. Lisäksi aiomme