Sisällysluettelo:

- Kirjoittaja John Day day@howwhatproduce.com.

- Public 2024-01-30 08:59.

- Viimeksi muokattu 2025-01-23 14:41.

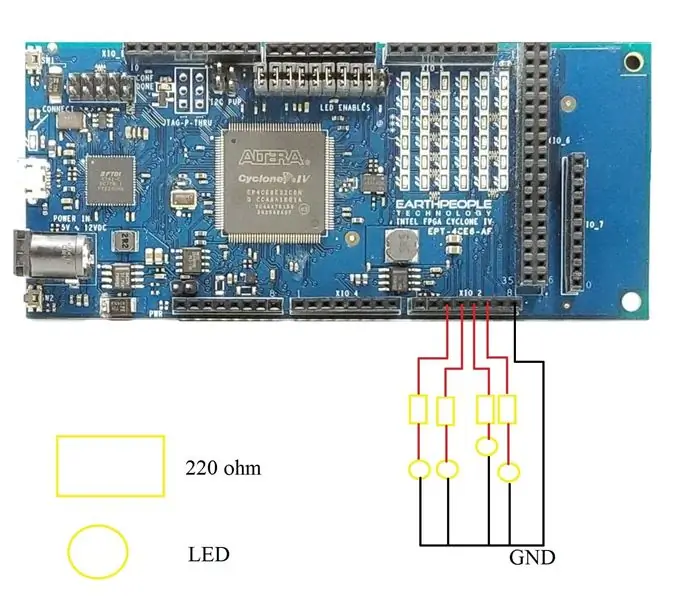

Tässä opetusohjelmassa aiomme käyttää FPGA: ta ulkoisen LED -piirin ohjaamiseen. Toteutamme seuraavat tehtävät

(A) Käytä FPGA Cyclone IV DuePrologicin painikkeita LED -valojen ohjaamiseen.

(B) Salaman merkkivalo syttyy ja sammuu säännöllisesti

Videon demo

Lab-valikko:

Vaihe 1: Rakenna elektroninen piiri

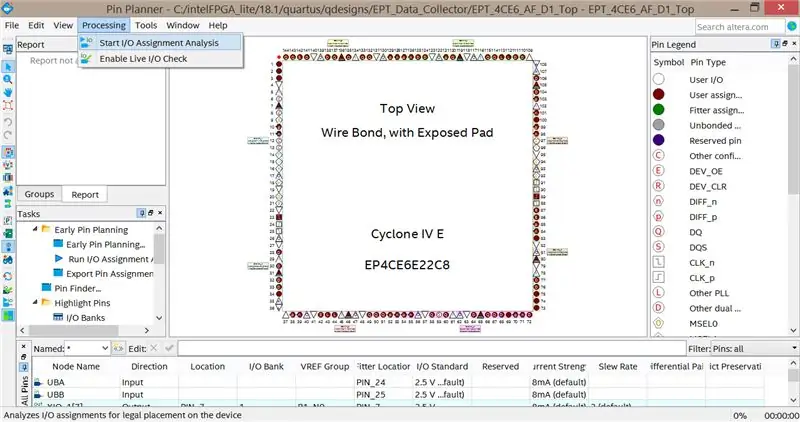

Vaihe 2: Tarkista Pin Planner ja muokkaa Verilog -koodia

Vaihe 3: Muokkaa Verilog -koodia

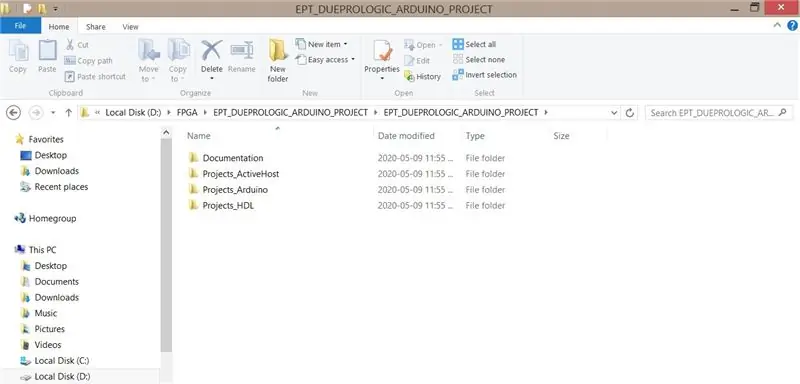

Kun ostat FPGA DueProLogicin, sinun pitäisi saada DVD. Kun olet avannut "Projects_HDL", sinun pitäisi nähdä alkuperäinen kooditiedosto

Lisää korostettu koodi. Se rekisteröi I/O -portit ja antaa porteille numeroita.

lähtöjohto [7: 0] XIO_1, // XIO-D2-D9

lähtöjohto [5: 0] XIO_2, // XIO-D10-D12

lähtöjohto [5: 0] XIO_3, // XIO-D22-D29

tulojohto [5: 0] XIO_4, // XIO-D30-D37

tulojohto [5: 0] XIO_5, // XIO-D38-D45

lähtöjohto [4: 0] XIO_6_OUT, // XIO-D46-D53

tulojohto [31: 5] XIO_6, // XIO-D46-D53

lähtöjohto [2: 0] XIO_7, // XIO - D69, D70, D71, D74, D75, D76

tulojohto UBA, // Painonappikytkimet

tulojohto UBB // Painonappikytkimet

anna XIO_1 [3] = start_stop_cntrl;

määritä XIO_2 [1] = start_blinky; // LED -salama LED päällä ja pois päältä

määritä XIO_2 [2] = 1'b1; // lähtö HIGH

määritä XIO_2 [3] = ~ UBA; // Painike A

määritä XIO_2 [4] = UBB; // Painike B

anna c_enable = XIO_5 [2];

määritä LEDExt = XIO_5 [5];

Sitten meidän on asetettava viiveajastin. Kommentoi alkuperäistä ajastinkoodia ja kirjoita uusi ajastintoiminto

//-----------------------------------------------

// LED Vilkkuva käynnistys

//-----------------------------------------------

/*

aina @(posedge CLK_66 tai negedge RST)

alkaa

jos (! RST)

start_blinky <= 1'b0;

muu

alkaa

jos (control_register [7: 4]> 0)

start_blinky <= 1'b1;

muu

start_blinky <= 1'b0;

loppuun

loppuun

*/

reg [31: 0] ex;

alku alkaa

ex <= 32'b0;

start_blinky <= 1'b0;

loppuun

aina @(postaus CLK_66)

alkaa

ex <= ex + 1'b1;

jos (esim.> 100000000) // salama päällä/pois ~ 1,6 sekuntia, kello 66MHz

alkaa

start_blinky <=! start_blinky;

ex <= 32'b0;

loppuun

loppuun

//-----------------------------------------------

// LED -viiveajastinlaskuri

//-----------------------------------------------

/*

aina @(asento CLK_66 tai reuna RST)

alkaa

jos (! RST)

led_viive_laskuri <= TIMER_LOW_LIMIT;

muu

alkaa

jos (ilmoita [SELECT_MODE])

led_viive_laskuri <= ajastimen_arvo;

muuten jos (tila [WAIT_FOR_TIMER])

led_viive_laskuri <= led_viive_laskuri - 1'd1;

loppuun

loppu*/

Vaihe 4: Käännä Verilog -koodi

Paina "Aloita kokoaminen" Quartuksessa, virheilmoitusta ei pitäisi luoda.

Jos saat virheilmoituksen useista nastoista. Siirry kohtaan Tehtävät -> Laite -> Laite- ja nastavaihtoehdot -> Kaksikäyttöiset nastat -> muuta sopivan nastan arvoksi "Käytä tavallisena I/O: na".

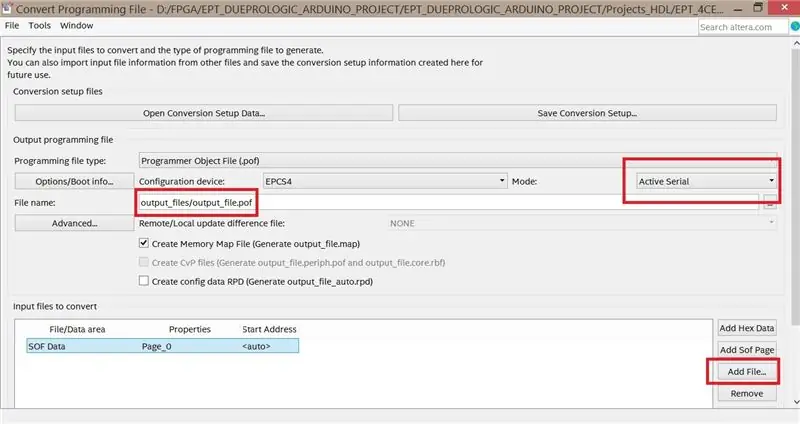

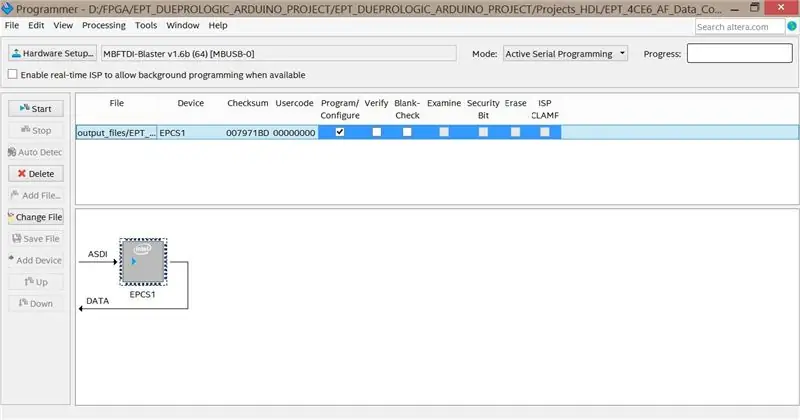

Kääntämisen jälkeen sinun pitäisi saada pof -tulostustiedosto suoraan. Jos ohjelmistosi ei ole ajan tasalla, saatat saada vain sof-tiedoston. Kun se tapahtuu, napsauta "Tiedosto" Quartus -> "muunna ohjelmointitiedostoja". Muuta asetuksia, jotka on merkitty punaisilla ruuduilla.

Vaihe 5: Kokeillaan

Loppujen lopuksi sen pitäisi toimia !!! Keltainen LED palaa aina. Punainen LED vilkkuu. Sininen LED -valo sammuu, jos painat painiketta B. Vihreä LED -valo syttyy, jos painat painiketta A.

Suositeltava:

FPGA Cyclone IV DueProLogic Controls Raspberry Pi -kamera: 5 vaihetta

FPGA Cyclone IV DueProLogic Controls Raspberry Pi -kamera: FPGA DueProLogic on virallisesti suunniteltu Arduinolle, mutta aiomme tehdä FPGA: sta ja Raspberry Pi 4B: stä kommunikoitavia. FPGA kääntää kulmaa

FPGA Cyclone IV DueProLogic Controls Servomoottori: 4 vaihetta

FPGA Cyclone IV DueProLogic Controls Servomoottori: Tässä opetusohjelmassa aiomme kirjoittaa Verilog -koodin servomoottorin ohjaamiseen. Servo SG-90 on Wavesharen valmistama. Kun ostat servomoottorin, saatat saada tietolomakkeen, jossa luetellaan käyttöjännite, suurin vääntömomentti ja ehdotettu pu

Arduino Cyclone Game: 5 vaihetta (kuvilla)

Arduino Cyclone Game: En ole koskaan pelannut todellista syklonipelipeliä, mutta pidän ajatuksesta pelata reaktioaikamme kanssa. Se koostuu 32 LEDistä, jotka muodostavat ympyrän, LEDit syttyvät yksitellen led -jahtajana. Tavoitteena on painaa nappia

Cyclone (Arduino LED Game): 6 vaihetta (kuvilla)

Cyclone (Arduino LED Game): Tässä opetusohjelmassa opetan sinulle, kuinka luoda LED -peli, jossa on hyvin vähän koodia tai kokemusta! Minulla oli tämä idea jonkin aikaa ja lopulta ryhdyin sen luomiseen. Se on hauska peli, joka muistuttaa meitä kaikkia arcade -pelejä. On myös muita opetusohjelmia

Cyclone LED Arcade Game: 4 vaihetta

Cyclone LED Arcade Game: Tämän projektin tarkoituksena oli luoda yksinkertainen peli Arduinolla, joka olisi interaktiivinen ja viihdyttävä lapsille. Muistan, että Cyclone -arcade -peli oli yksi suosikki arcade -peleistäni nuorempana, joten päätin toistaa sen. T