Sisällysluettelo:

- Kirjoittaja John Day day@howwhatproduce.com.

- Public 2024-01-30 09:03.

- Viimeksi muokattu 2025-01-23 14:44.

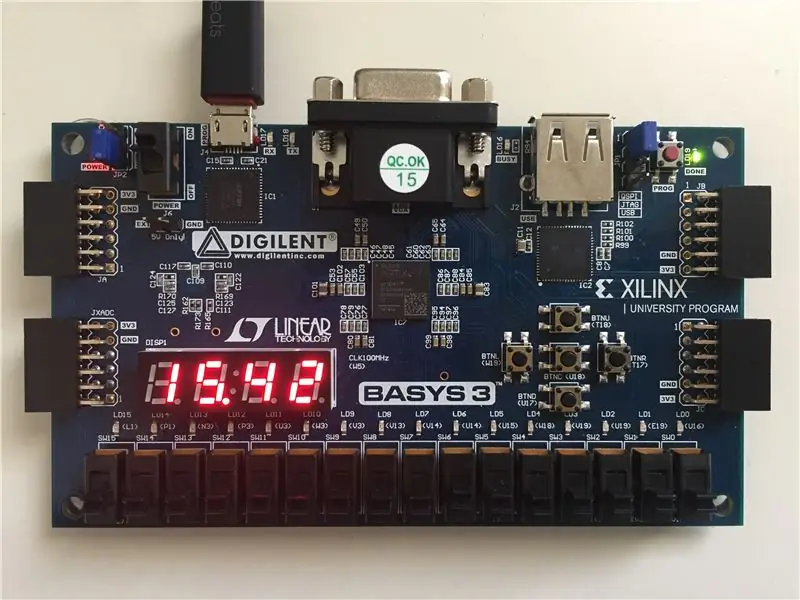

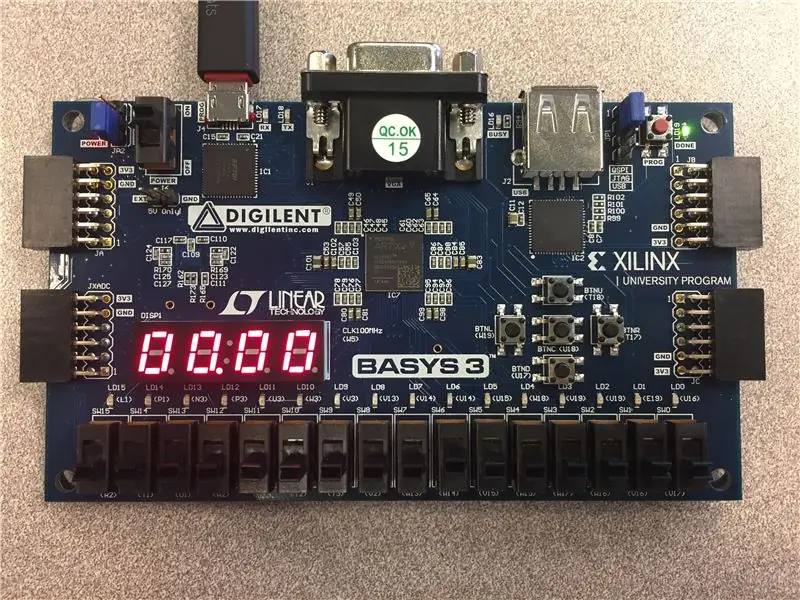

Tämä on opetusohjelma sekuntikellon tekemisestä VHDL- ja FPGA-piirilevyllä, kuten Basys3 Atrix-7 -kortilla. Sekuntikello voi laskea 00,00 sekunnista 99,99 sekuntiin. Se käyttää kahta painiketta, toinen käynnistys-/pysäytyspainikkeelle ja toinen nollauspainikkeelle. Numerot näytetään kortin seitsemän segmentin näytöllä sen anodeja ja katodeja käyttäen. Tämän sekuntikellon toimimiseksi tarvitaan kolme eri tiedostoa.

Vaihe 1: Laitteisto/ohjelmisto

- Basys3 Atrix-7 FPGA -levy

- Xilinxin Vivado Design Suite

- USB 2.0 A uros-Micro-B uros

Vaihe 2: Lohkokaavio

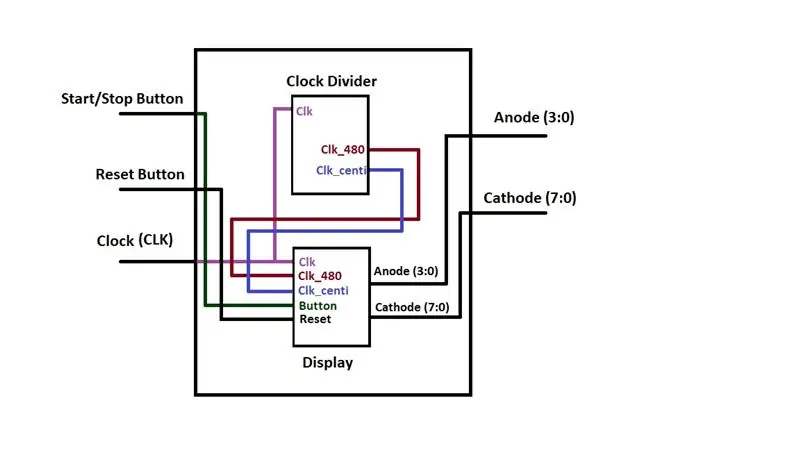

Sekuntikellossa on kolme tuloa ja kaksi lähtöä. Kolme tuloa ovat käynnistys/pysäytys, nollaus ja kello. Käynnistys/pysäytys ja nollaus ovat painikkeita ja kello on levyn 100 MHz: n kello. Kaksi lähtöä ovat seitsemän segmentin näytön anodit ja katodit.

Ensimmäisessä moduulissa (kellonjakaja) on yksi tulo ja kaksi lähtöä. Tulo on kortin 100 MHz: n kello ja lähdöt ovat kaksi erillistä kelloa, joista toinen toimii 480 Hz: llä ja toinen 0,5 MHz: llä.

Toisessa moduulissa (näyttö) on viisi tuloa ja kaksi lähtöä. Tulot ovat kortin 100 MHz: n kello, kaksi kellonjakamoduulin kelloa sekä käynnistys/pysäytys- ja nollauspainikkeet. Lähdöt ovat anodit ja katodit.

Viimeisessä moduulissa (koko lohkokaavion mallintama) on kolme tuloa ja kaksi lähtöä. Tämä tiedosto kokoaa kaiken yhteen. Tulot ovat levyn 100 MHz ja käynnistys/pysäytys- ja nollauspainikkeet. Lähdöt ovat anodeja ja katodeja, jotka ohjaavat seitsemän segmentin näyttöä. Kaikki tulot ja lähdöt ovat fyysisesti viimeisen moduulin piirilevyssä.

Vaihe 3: Tilakaavio

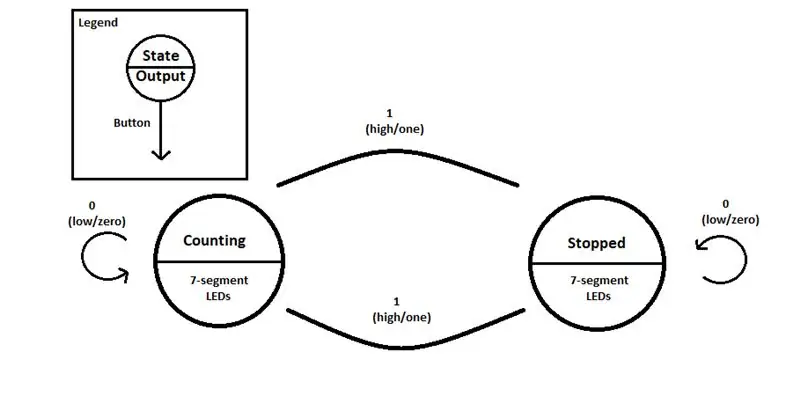

Yllä oleva kuva näyttää sekuntikellon toimintakaavion. Palautuspainikkeen painaminen ei vaikuta sekuntikellon tilaan. Seuraava tila määritetään käynnistys-/pysäytyspainikkeella. Käynnistys/pysäytys on "HIGH", kun sitä painetaan alas, mutta ei silloin, kun sitä pidetään painettuna, ja "LOW", kun painike on palautunut taaksepäin tai sitä pidetään painettuna hetken "HIGH" ollessa.

Jos sekuntikello laskee ja käynnistys-/pysäytyspainike on "HIGH", se lopettaa laskennan. Jos sekuntikello pysäytetään ja käynnistys-/pysäytyspainike on "HIGH", se alkaa laskea uudelleen. Jos molemmissa tiloissa käynnistys-/pysäytyspainike on "LOW", se pysyy siinä tilassa, jossa se on tällä hetkellä.

Vaihe 4: Kellonjakamoduuli

Kellonjakamoduulissa on yksi tulo, kortin 100 MHz: n kello ja kaksi lähtöä, 480 Hz: n ja 0,5 MHz: n kellot. 480 Hz: n kelloa käytetään pitämään kaikki seitsemän segmentin näytön LED-valot "päällä" samanaikaisesti vaihtamalla neljä nopeasti. 0,5 megahertsin kelloa käytetään sekuntikellon todelliseen laskemiseen senttisekunteina.

Vaihe 5: Näyttömoduuli

Tässä näyttömoduulissa on viisi tuloa, kortin 100 MHz: n kello, kaksi kellomoduulin kelloa ja käynnistys/pysäytys- ja nollauspainikkeet sekä kaksi lähtöä, anodit ja katodit. Tässä moduulissa on myös "logiikka", jolla sekuntikello laskee ja sisältää äärellisen tilan koneen.

Vaihe 6: Sidosmoduuli

Tämä viimeinen moduuli yhdistää kaksi muuta moduulia yhteen. Siinä on kolme tuloa, levyn 100 MHz: n kello ja käynnistys/pysäytys- ja nollauspainikkeet sekä kaksi lähtöä, anodit ja katodit. 100 MHz: n kello siirtyy kellonjakamoduuliin ja näyttömoduuliin, ja käynnistys/pysäytys- ja nollauspainikkeet siirtyvät näyttömoduuliin. Kellonjakoyksikön lähdöt (480Hz ja 0,5MHz) menevät näyttömoduulin kahteen kellotuloon. Näyttömoduulin lähdöt (anodit ja katodit) menevät lopullisen moduulin lähtöihin.

Vaihe 7: Rajoitukset

Kaksi tuloa voi olla mikä tahansa Basys3 Atrix-7 FPGA -kortin painike, ja ulostulot ovat neljä anodia ja kahdeksan katodia (koska haluat myös desimaalipilkun sekuntien ja millisekuntien välillä) seitsemän segmentin näytössä.

Vaihe 8: Valmis

Lataa ohjelma Basys3 Atrix-7 FPGA -kortillesi ja paina käynnistys-/pysäytyspainiketta käynnistääksesi sekuntikello!

Suositeltava:

Cordic -algoritmi VHDL: n avulla: 4 vaihetta

Cordic -algoritmi VHDL: n avulla: ## Tämä on Googlen suosituin linkki CORDIC ALGORITHM: n VHDL -toteutukseen sini- ja kosini -aallon luomiseksi ## Tällä hetkellä on olemassa monia laitteistotehokkaita algoritmeja, mutta nämä eivät ole hyvin tunnettuja, koska pehmeän sodan valta

Yksinkertaisen nelisuuntaisen yhdistetyn välimuistiohjaimen suunnittelu VHDL: ssä: 4 vaihetta

Yksinkertaisen nelisuuntaisen yhdistetyn välimuistiohjaimen suunnittelu VHDL: ssä: Edellisessä ohjeessani näimme kuinka suunnitella yksinkertainen suoraan kartoitettu välimuistiohjain. Tällä kertaa mennään askel eteenpäin. Suunnittelemme yksinkertaisen nelisuuntaisen yhdistetyn välimuistiohjaimen. Etu? Vähemmän miss -korkoa, mutta perfo -kustannuksella

Ohjelmoitavan keskeytysohjaimen suunnittelu VHDL: ssä: 4 vaihetta

Ohjelmoitavan keskeytysohjaimen suunnittelu VHDL: ssä: Olen hämmästynyt siitä, millaisia vastauksia saan tästä blogista. Kiitos kaverit vierailustani blogissani ja kannustivat minua jakamaan tietoni kanssanne. Tällä kertaa aion esitellä toisen mielenkiintoisen moduulin suunnittelun, jonka näemme kaikissa SOC -järjestelmissä - Keskeytä C

Yksinkertaisen välimuistiohjaimen suunnittelu VHDL: ssä: 4 vaihetta

Yksinkertaisen välimuistiohjaimen suunnittelu VHDL: ssä: Kirjoitan tämän ohjeellisen, koska minusta oli hieman vaikeaa saada viite -VHDL -koodi oppia ja aloittaa välimuistiohjaimen suunnittelu. Joten suunnittelin välimuistiohjaimen itse tyhjästä ja testasin sen onnistuneesti FPGA: lla. Minulla on p

PID -ohjain VHDL: 10 vaihetta

PID -ohjain VHDL: Tämä projekti oli viimeinen projektini, jolla suoritin kunnia -alemman korkeakoulututkinnon Cork Institute of Technologysta. Tämä opetusohjelma on jaettu kahteen osaan, joista ensimmäinen kattaa PID -koodin pääosan, joka on projektin päätarkoitus ja