Sisällysluettelo:

- Kirjoittaja John Day day@howwhatproduce.com.

- Public 2024-01-30 09:00.

- Viimeksi muokattu 2025-01-23 14:41.

Kirjoittanut AmCoderhttps://www.linkedin.com/in/mitu

Tietoja: Mitu Raj - vain harrastaja ja oppija - sirusuunnittelija - ohjelmistokehittäjä - fysiikan ja matematiikan harrastaja Lisätietoja AmCoderista »

## Tämä on Googlen suosituin linkki CORDIC ALGORITHM: n VHDL -toteutukseen sini- ja kosini -aallon luomiseksi ## Tällä hetkellä on olemassa monia laitteistotehokkaita algoritmeja, mutta niitä ei tunneta hyvin, koska ohjelmistojärjestelmät ovat hallitsevia monta vuotta. CORDIC on sellainen algoritmi, joka on vain joukko siirto- ja lisäyslogiikkaa, jota käytetään monenlaisten toimintojen laskemiseen, mukaan lukien tietyt trigonometriset, hyperboliset, lineaariset ja logaritmiset funktiot. Tämä on algoritmi, jota käytetään laskimissa jne. Näin ollen vain yksinkertaisia vaihtajia ja lisäyksiä käyttämällä voimme suunnitella laitteiston, jolla on vähemmän monimutkaisuus, mutta DSP: n teho, käyttämällä johdollista algoritmia. Siksi se voidaan suunnitella paljaana RTL -mallina VHDL: ssä tai Verilogissa ilman erillisiä liukulukuyksiköitä tai monimutkaisia matemaattisia IP -osoitteita.

Vaihe 1: VHDL ja Modelsim

Tässä sydämen algoritmi toteutetaan VHDL: n avulla sini- ja cose -aallon luomiseksi. Se voi tulostaa syöttökulman sinin ja kosinin erittäin tarkasti. Koodi voidaan syntetisoida FPGA: lla. Modelsim -mallia käytetään simuloimaan suunnittelua ja testipenkkiä.

Vaihe 2: VHDL -koodi suunnittelulle ja testipenkille

Binaarista skaalaustekniikkaa käytetään edustamaan liukulukuja.

Käy oheisten asiakirjojen läpi ennen koodin kirjoittamista.

Siirry läpi simuloimalla cordic_v4.vhd - Suunnittelu -Tulo on kulma 32 bittiä + merkkibitti; se voi käsitellä mitä tahansa kulmaa 0-+/- 360 astetta sisääntulon tarkkuudella 0,000000000233 astetta. Syötettäessä -> MSB on merkkibitti ja loput 32 bittiä edustavat suuruusluokkaa. tarkasti 0,00001526. Huomaa, että lähtö näytetään 2: n kohteliaisuusmuodossa, jos vastaava sini- tai cos -arvo on negatiivinen. Testb.vhd: n simulointi - suunnittelupenkki (1) Syöttökulmat ja vedon nollaus = '0'. Kahden simulointivaiheen jälkeen vedä palautus arvoon '1' ja "suorita kaikki". (2) Aseta simulaatioikkunassa sini- ja cos -signaalien säde desimaaliksi ja muotoksi> Analoginen (automaattinen). (3) Loitonna nähdäksesi aaltomuodon asianmukaisesti.

Vaihe 3: Liitetyt tiedostot

(1) cordic_v4.vhd - Suunnittelu. (2) testb.vhd - Suunnittelupenkki.

(3) Asiakirja siitä, miten pakottaa kulmatulot ja muuntaa binääriset tulokset.

Päivitys: NÄMÄ TIEDOSTOT OVAT SULJETTUJA, EI TOIMITETAAN ENÄÄ. KÄYTÄ TIEDOSTOJA SEURAAVASTA VAIHEESTA

Vaihe 4: Mini -Cordic IP Core - 16 -bittinen

Yllä olevan toteutuksen rajoitus on hidas, alhaisempi kellotaajuus, koska laskutoimitukset suoritetaan yhdessä kellosyklissä. Mini-Cordic IP Core- 16 Bit

- Kriittiset reitit jaettu useisiin sykleihin suorituskyvyn parantamiseksi.- Nopeampi- FPGA: n todistettu muotoilu syntetisoitu jopa 100 Mhz: n kelloon.- Enemmän aluetta optimoitu HDL: ssä, vähemmän laitteistoa.- Lisätty kuormitus- ja valmiustilasignaalit.- Ainoa haittapuoli on pienempi resoluutio verrattuna edellinen. Testipenkki:

täysin automatisoitu 0 - 360 asteen kulmatuloista

Liitetiedostot: 1) mini -cordic -päävdl -tiedosto 2) mini -cordic -testipenkki 3) Mini Cordic IP Core -opas 4) Asiakirja kulmien pakottamisesta ja tulosten muuntamisesta

Jos sinulla on kysyttävää, ota rohkeasti yhteyttä minuun:

Mitu Raj

seuraa minua:

sähköposti: iammituraj@gmail.com

### Latauksia yhteensä: 325 1.5.2021 asti ###

### Koodia muokattu viimeksi: 07.07.2020 ###

Suositeltava:

Hallitse talon valoja Google Assistantin avulla Arduinon avulla: 7 vaihetta

Hallitse talon valoja Google Assistantin avulla Arduinon avulla: (Päivitys 22.8.2020: Tämä ohje on 2 vuotta vanha ja perustuu joihinkin kolmansien osapuolien sovelluksiin. Kaikki heidän puolellaan tehdyt muutokset saattavat tehdä projektista toimimattoman. Se voi olla tai ei työskentele nyt, mutta voit seurata sitä viitteenä ja muokata sen mukaan

Useiden ESP-keskustelujen tekeminen ESP-NOW: n avulla ESP32: n ja ESP8266: n avulla: 8 vaihetta

Useiden ESP-keskustelujen tekeminen ESP-NYT: n avulla ESP32: n ja ESP8266: n avulla: Käynnissä olevassa projektissani tarvitsen useita ESP: itä puhuakseni keskenään ilman reititintä. Tätä varten käytän ESP-NOW-ohjelmaa langattoman viestinnän tekemiseen keskenään ilman ESP: n reititintä

Ihmisen ja tietokoneen käyttöliittymä: Function a Gripper (valmistaja Kirigami) ranneliikkeen avulla EMG: n avulla: 7 vaihetta

Ihmisen ja tietokoneen käyttöliittymä: Function a Gripper (valmistaja Kirigami) ranneliikkeen avulla EMG: n avulla: Joten tämä oli ensimmäinen kokeiluni ihmisen ja tietokoneen välisessä käyttöliittymässä. pythonin ja arduinon kautta ja käytti origamipohjaista tarttujaa

Perus sekuntikello VHDL: n ja Basys3 Boardin avulla: 9 vaihetta

Perus sekuntikello VHDL- ja Basys3 -korttien avulla: Tervetuloa opastamaan sekuntikellon rakentaminen perus VHDL- ja Basys 3 -levyjä käyttäen. Olemme innoissamme voidessamme jakaa projektimme kanssasi! Tämä oli viimeinen projekti CPE 133 (Digital Design) -kurssille Cal Poly, SLO: ssa syksyllä 2016. Hanke, jonka rakennamme

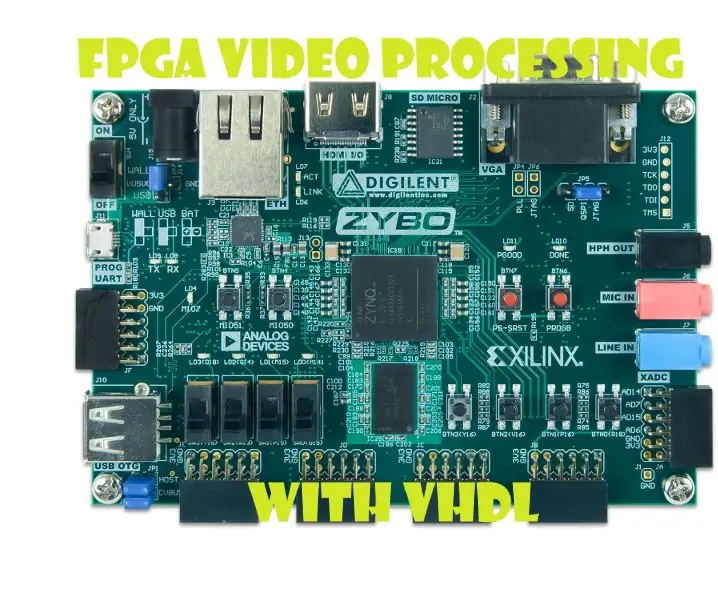

Videon käsittely VHDL: n ja Zybo: n avulla: 10 vaihetta

Videon käsittely VHDL: n ja Zyboyn avulla: FPGA: t ovat nopeampia kuin suorittimet, koska ne voivat tehdä monia laskelmia rinnakkain Huomautus: Tämä projekti on vielä rakenteilla ja sitä parannetaan (heti kun minulla on aikaa). Samaan aikaan matkustan ympäri maailmaa