Sisällysluettelo:

- Kirjoittaja John Day day@howwhatproduce.com.

- Public 2024-01-30 09:01.

- Viimeksi muokattu 2025-01-23 14:42.

Analysoin, miten DC-DC Technologies vastaa haasteelliseen virtalähteen suunnitteluun.

Sähköjärjestelmien suunnittelijat joutuvat jatkuvasti markkinoiden paineille löytääkseen tapoja hyödyntää käytettävissä olevaa sähköä parhaalla mahdollisella tavalla. Kannettavissa laitteissa suurempi tehokkuus pidentää akun käyttöikää ja tuo enemmän toimintoja pienempiin paketteihin. Palvelimilla ja tukiasemilla tehokkuuden paraneminen voi säästää suoraan infrastruktuuria (jäähdytysjärjestelmät) ja käyttökustannuksia (sähkölaskut). Vastatakseen markkinoiden vaatimuksia järjestelmäsuunnittelijat parantavat tehonmuutosprosesseja monilla aloilla, mukaan lukien tehokkaammat kytkentätopologiat, pakettiinnovaatiot ja uudet piikarbidiin (SiC) ja galliumnitridiin (GaN) perustuvat puolijohdelaitteet.

Vaihe 1: Vaihtomuuntimen topologian parantaminen

Saadakseen kaiken hyödyn irti käytettävissä olevasta tehosta ihmiset omaksuvat yhä enemmän malleja, jotka perustuvat kytkentätekniikkaan lineaarisen tekniikan sijasta. Kytkentävirtalähteen (SMPS) tehollinen teho on yli 90%. Tämä pidentää kannettavien järjestelmien akun käyttöikää, alentaa suurten laitteiden sähkökustannuksia ja säästää tilaa, jota aiemmin käytettiin jäähdytyselementtien osissa.

Vaihdettuun topologiaan siirtymisellä on tiettyjä haittoja, ja sen monimutkaisempi muotoilu edellyttää suunnittelijoilta useita taitoja. Suunnittelijoiden on tunnettava analogiset ja digitaaliset tekniikat, sähkömagneetti ja suljetun silmukan ohjaus. Piirilevyjen (PCB) suunnittelijoiden on kiinnitettävä enemmän huomiota sähkömagneettisiin häiriöihin (EMI), koska suurtaajuiset kytkentäaaltomuodot voivat aiheuttaa ongelmia herkissä analogisissa ja RF -piireissä.

Ennen transistorin keksimistä ehdotettiin kytkinmuotoisen tehonmuuntamisen peruskäsitettä: esimerkiksi vuonna 1910 keksitty Kate-tyyppinen induktiivinen purkausjärjestelmä, joka käytti mekaanista tärytintä toteuttaakseen flyback-tehostusmuuntimen autojen sytytysjärjestelmään.

Useimmat vakiotopologiat ovat olleet olemassa jo vuosikymmeniä, mutta tämä ei tarkoita, että insinöörit eivät säätäisi vakiomalleja uusien sovellusten, erityisesti ohjaussilmukoiden, mukauttamiseksi. Vakioarkkitehtuuri käyttää kiinteää taajuutta vakiolähtöjännitteen ylläpitämiseksi syöttämällä osan lähtöjännitteestä (jännitemoodin ohjaus) tai ohjaamalla indusoitua virtaa (nykyisen tilan ohjaus) eri kuormitusolosuhteissa. Suunnittelijat kehittyvät jatkuvasti voittaakseen perussuunnittelun puutteet.

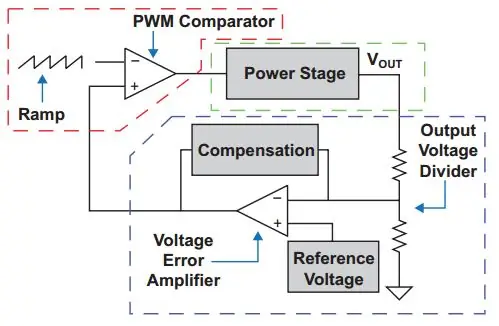

Kuva 1 on lohkokaavio suljetun silmukan perusjännitemoodin ohjausjärjestelmästä (VMC). Tehoaste koostuu virtakytkimestä ja lähtösuodattimesta. Kompensointilohko sisältää lähtöjännitteen jakajan, virhevahvistimen, vertailujännitteen ja silmukan kompensointikomponentin. Pulssileveysmodulaattori (PWM) vertaa vertailusäädintä virhesignaaliin kiinteään ramppisignaaliin tuottaakseen tulosignaalin, joka on verrannollinen virhesignaaliin.

Vaikka VMC -järjestelmän eri kuormilla on tiukat lähtösäännöt ja ne on helppo synkronoida ulkoisen kellon kanssa, vakioarkkitehtuurilla on joitain haittoja. Silmukan kompensointi vähentää ohjaussilmukan kaistanleveyttä ja hidastaa ohimenevää vastetta; virhevahvistin lisää käyttövirtaa ja vähentää tehokkuutta.

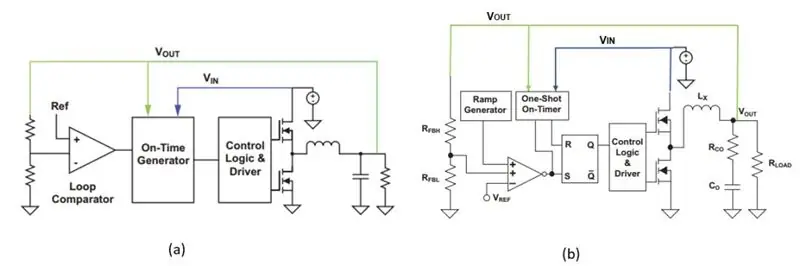

Jatkuva on-time (COT) -ohjausjärjestelmä tarjoaa hyvän ohimenevän suorituskyvyn ilman silmukan kompensointia. COT-ohjaus käyttää vertailijaa vertaamaan säädettyä lähtöjännitettä vertailujännitteeseen: kun lähtöjännite on pienempi kuin vertailujännite, syntyy kiinteä aika-pulssi. Pienillä käyttöjaksoilla tämä aiheuttaa kytkentätaajuuden olevan erittäin korkea, joten mukautuva COT-ohjain luo ajo- ja tulo- ja lähtöjännitteiden mukaan vaihtelevan ajan, joka pitää taajuuden lähes vakiona vakaassa tilassa. Texas Instrumentin D-CAP-topologia on parannus mukautuvaan COT-lähestymistapaan: D-CAP-ohjain lisää ramppijännitteen palautteen vertailutuloon, mikä parantaa värinän suorituskykyä vähentämällä sovelluksen kohinaa. Kuva 2 on COT- ja D-CAP-järjestelmien vertailu.

Kuva 2: COT-vakiotopologian (a) ja D-CAP-topologian (b) vertailu (Lähde: Texas Instruments) D-CAP-topologiasta on useita eri versioita eri tarpeisiin. Esimerkiksi TPS53632-puolisilta PWM-ohjain käyttää D-CAP+ -arkkitehtuuria, jota käytetään pääasiassa suurvirtaisissa sovelluksissa ja joka voi ohjata jopa 1 MHz: n tehotasoja 48V-1V POL-muuntimissa jopa 92%: n hyötysuhteella.

Toisin kuin D-CAP, D-CAP+ palautelenkki lisää komponentin, joka on verrannollinen indusoituun virtaan tarkan pudotuksen ohjaamiseksi. Lisääntynyt virhevahvistin parantaa DC -kuorman tarkkuutta eri linja- ja kuormitusolosuhteissa.

Ohjaimen lähtöjännite asetetaan sisäisellä DAC: lla. Tämä sykli alkaa, kun nykyinen takaisinkytkentä saavuttaa virhejännitetason. Tämä virhejännite vastaa vahvistettua jännite -eroa DAC -asetuspistejännitteen ja takaisinkytkennän lähtöjännitteen välillä.

Vaihe 2: Paranna suorituskykyä kevyessä kuormituksessa

Kannettavien ja puettavien laitteiden suorituskykyä on parannettava kevyessä kuormituksessa akun käyttöiän pidentämiseksi. Monet kannettavat ja puettavat sovellukset ovat virransäästötilassa "tilapäinen lepotila" tai "lepotila" valmiustilassa suurimman osan ajasta, ja ne aktivoidaan vain käyttäjän syöttämien tai määräaikaisten mittausten perusteella, joten minimoi virrankulutus valmiustilassa. Se on ykkösprioriteetti.

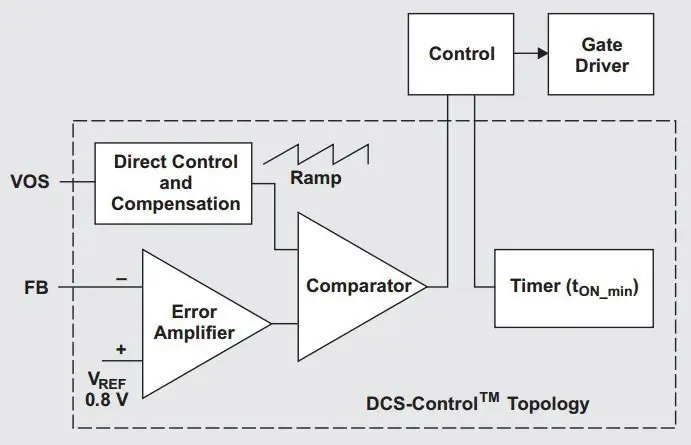

DCS-ControlTM (Direct Control to Saumaton siirtyminen energiansäästötilaan) -opologiassa yhdistyvät kolmen eri ohjausjärjestelmän (eli hystereesitilan, jännitetilan ja virtatilan) edut, jotka parantavat suorituskykyä pienissä kuormitusolosuhteissa, erityisesti siirtyessä tai kun poistuminen kevyestä kuormitustilasta. Tämä topologia tukee PWM -tiloja keskisuurille ja raskaille kuormille sekä virransäästötilaa (PSM) kevyille kuormille.

PWM -käytön aikana järjestelmä toimii nimelliskytkentätaajuudellaan syöttöjännitteen perusteella ja ohjaa taajuuden muutosta. Jos kuormitusvirta pienenee, muunnin siirtyy PSM: ään ylläpitääkseen suurta hyötysuhdetta, kunnes se laskee hyvin kevyeen kuormaan. PSM: ssä kytkentätaajuus pienenee lineaarisesti kuormitusvirran myötä. Molempia tiloja ohjataan yhdellä ohjauslohkolla, joten siirtyminen PWM: stä PSM: ään on saumatonta eikä vaikuta lähtöjännitteeseen.

Kuva 3 on DCS-ControlTM: n lohkokaavio. Ohjaussilmukka kerää tietoa lähtöjännitteen muutoksesta ja syöttää sen suoraan takaisin nopealle vertailijalle. Vertailija asettaa kytkentätaajuuden (vakiona vakiotilan käyttöolosuhteissa) ja antaa välittömän vastauksen dynaamisiin kuormituksen muutoksiin. Jännitteen takaisinkytkentäsilmukka säätää tarkasti DC -kuorman. Sisäisesti kompensoitu säätöverkko mahdollistaa nopean ja vakaan toiminnan pienillä ulkoisilla komponenteilla ja alhaisilla ESR -kondensaattoreilla.

Kuva 3: DCS-ControlTM-topologian käyttöönotto TPS62130-buck-muuntimessa (Lähde: Texas Instruments)

Synkroninen kytkentätehon muunnin TPS6213xA-Q1 perustuu DCS-ControlTM-topologiaan ja on optimoitu suuritehoisille POL-sovelluksille. Tyypillinen 2,5 MHz: n kytkentätaajuus mahdollistaa pienten induktorien käytön ja tarjoaa nopean ohimenevän vasteen ja korkean lähtöjännitteen tarkkuuden. TPS6213 toimii syöttöjännitealueella 3V - 17V ja voi tuottaa jopa 3A jatkuvaa virtaa 0,9V - 6V lähtöjännitteen välillä.

Suositeltava:

MITEN AJATA FT232R USB UART CLONE ARDUINO NANO BOARD 3.0: 7 vaihetta

MITEN AJATA FT232R USB UART CLONE ARDUINO NANO BOARD 3.0: Tänään ostin arduino nano v3.0 (klooni), mutta minulla on ongelma. tietokoneeni tunnistaa aina " FT232R USB UART " andarduino Ide ei tunnista tätä korttia. miksi? mikä hätänä? okei, minulla on opetusohjelma tämän ongelman ratkaisemiseksi

DIY Bluetooth Boombox -kaiutin - MITEN: 13 vaihetta (kuvilla)

DIY Bluetooth Boombox -kaiutin | MITEN: Hei! Kiitos, että katsoit tämän projektin, tämä on suosikkiluettelossani! Olen erittäin iloinen saadessani tämän hämmästyttävän projektin. Projektin aikana on käytetty monia uusia tekniikoita kehityksen yleisen laadun ja viimeistelyn parantamiseksi

Suunnittele pahvikuppi suunnittelun ajattelumenetelmillä: 7 vaihetta

Suunnittele pahvikuppi suunnitteluajattelumenetelmillä: Hei, Pahvikuppi, joka on suunniteltu suunnitteluajattelumenetelmien mukaisesti, täällä. Katsokaa tätä ja kommentoikaa. Parannan projektiani kommenteillasi :) Kiitos paljon ---------------------------- Merhaba, Design ajattelee minua

Projekti 2: Suunnittelun kääntäminen: 11 vaihetta (kuvilla)

Projekti 2: Suunnittelun kääntäminen: Hei harrastusmies, Hyvä ystäväni oli koonnut useita komponentteja yhdessä Raspberry Pi: n kanssa purkamaan RS232 -protokollan TTL: ksi. Lopputulos heitettiin kaikki laatikkoon, joka sisälsi 3 pääkomponenttia: tehomuuntimen teholähteeksi

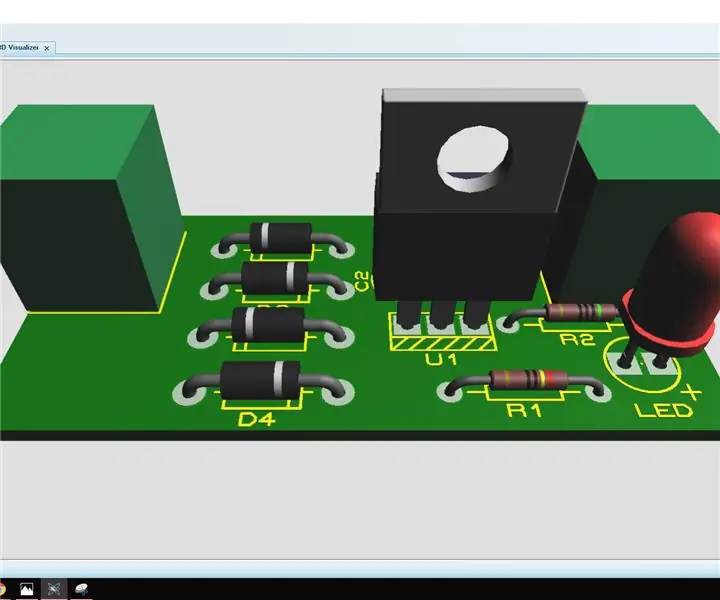

Piirien ja piirilevyn suunnittelun simulointi Proteuksessa: 10 vaihetta

Piirien+piirilevyn suunnittelun simulointi Proteuksella: Tämä on vaiheittainen ohje insinööreille ja harrastajille. Tässä ohjeessa keskustelen piirisimulaatioista & Piirilevyjen suunnittelu Proteus 8: ssa, lopuksi keskustelen myös sähköpiirien etsauksesta 5 minuutin kuluessa